# Pre-Silicon Safety-Related Functional Verification of Automotive Smart Power ICs Using the Fault Injection Technique

## Özlem Karaca

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Universität der Bundeswehr München zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation.

### Gutachter:

- 1. Prof. Dr. techn. Linus Maurer

- 2. Prof. Dr. rer. nat. Georg Pelz

Die Dissertation wurde am 12. 04. 2017 bei der Universität der Bundeswehr München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 05. 09. 2017 angenommen. Die mündliche Prüfung fand am 23. 10. 2017 statt.

# Acknowledgement

First and foremost I would like to thank my doctoral advisors Prof. Dr. Linus Maurer and Prof. Dr. Georg Pelz for supervising my research work. Thank you for your support and guidance from an academic as well as industrial perspective.

I'd like to thank the members of the Automotive Design Methodology group at IFX Munich and Bucharest Jerome Kirscher, Matthias Kunze, Dr. Monica Rafaila, Dr. Manuel Harrant, Dr. Andi Buzo, Ciprian Ivu Petru and Dr. Thomas Nirmaier for supporting my work and being great colleagues. I appreciate your accomplishments on which I was able to build on. Moreover, I'd like to thank Dr. Thomas Rickes and my fellow doctoral candidates Dr. Klaus Hoermaier and Sebastian Simon for your contributions to my work.

From the IFX sites in Villach and Padova, I'd like to thank Arnaud Laroche, Andreas Tributsch, Roland Lengfeldner, Stefano Orlandi, Christian Garbossa, Enrico Orietti and Filippo Mele for supporting my work and giving me the opportunity to establish a sound basis for my work in real projects.

Finally, I would like to express my special thanks and appreciation to my husband Lukas, my family and friends for their support during my education.

## Abstract

The increasing demand for electrification of automotive systems with electronic control units (ECUs) is driven by automotive trends such as electromobility and autonomous driving. However, the functional complexity of modern analog/-mixed-signal integrated circuits (ICs) causes an increasing risk from random hardware failures in the electronics. Even more for safetyrelated applications, the presence of a hardware failure in the IC may have severe consequences for humans and environment. Safety-related ICs such as Smart Power ICs must ensure a safe operating state even in the presence of a random hardware failure. For this purpose, the ICs implement diagnostic capability by safety mechanisms which prevent random hardware failures from causing hazard. Recently, this topic has come to the focus of interest in semiconductor companies due to the advent of the functional safety standard for road vehicles, ISO 26262. The standard provides a framework of requirements which affects the whole development process of safety-related ICs due to which semiconductor companies face new challenges in terms of compliance.

The pre-silicon functional verification is generally a crucial stage within the IC development. It allows to detect functional misalignments between the circuit's required and actual behaviour before manufacturing. In this context, the standard explicitly requires a simulation-based method utilizing the fault injection technique. The purpose of this method is to evaluate the circuit in the presence of hardware failures in terms of diagnostic capability and compliance with functional requirements.

Fault injection and simulation of analog/mixed-signal circuits has been a challenging task since the early 90s. This is mainly due to the lack of a generally accepted definition of fault coverage and corresponding fault models. Additionally, thorough fault simulation with the transistor-level netlist becomes infeasible for the top-level circuit. Moreover, commercially available computer-aided design tools do not yet offer a feature for automatizing the fault injection technique for analog/mixed-signal circuits. Thus, this task requires so far labour-intensive manual effort. In order to utilize the fault injection technique for pre-silicon safety-related functional verification of analog/mixed-signal circuits, the above mentioned challenges must be addressed by an adequate methodology.

The work presented in this thesis facilitates integration and automation of the fault injection technique in the electronic design automation tool Cadence<sup>®</sup> Virtuoso<sup>®</sup>. A fault model library is developed comprising diverse fault models which facilitate fault injection at different levels of abstraction of the circuit design. As an initial approach to safety-related verification, the

informal safety analysis method Failure Mode, Effects and Diagnosis Analysis (FMEDA) is utilized to structure the safety-related verification plan. Subsequently, a hierarchical fault injection approach is presented for efficient toplevel verification by skipping redundant fault simulation runs. This approach is based on fast component-level fault simulations and the determination of functional equivalent faults. Functional fault equivalence is determined by a clustering algorithm which processes simulated component-level circuit responses in order to find similarities among the waveforms. Eventually, functional equivalent faults must not be simulated repeatedly for top-level verification. Finally, soft faults by means of parametric and soft-structural fault models are considered for fault injection with variable parametrization. Their effects in the circuit are evaluated by means of global sensitivity analysis. Sensitivity indices are calculated which quantify the contribution of each soft fault to the variability of the circuit response. The sensitivity indices are used to rank faults and identify non-influential soft faults. A statistical significance test is exercised in order to eliminate non-significant faults from the soft fault list. Moreover, the cumulative contribution of each soft fault to the variability of the circuit response is used to further eliminate soft faults by keeping only those in the soft fault list which account for most of the variability. Although this approach reduces the soft fault coverage, most of the output variability due to soft faults in maintained for the verification.

Experimental results are presented for safety-related functional verification of an automotive high-voltage Lithium-ion cell balancing and monitoring module and a general purpose gate driver circuit which is a safety-related module of an automotive System-on-Chip (SoC). Finally, the work is concluded and an outlook is given.

## Abstrakt

Der steigende Bedarf an elektrifizierten Systemen im Automobil durch elektronische Kontrolleinheiten, engl. Electronic Control Units (ECUs), wird angetrieben durch Trends wie Elektromobilität und autonomes Fahren. Gleichzeitig steigt die funktionale Komplexität moderner integrierter Analog/Mixed-Signal-Schaltungen (AMS ICs), wodurch sich auch das Risiko für das Auftreten eines zufälligen Hardwarefehlers, engl. Random Hardware Failure, in der Elektronik erhöht. Dies gilt insbesondere für sicherheitsrelevante Applikationen, in denen ein Hardwarefehler schwerwiegende Konsequenzen für Mensch und Umwelt haben kann. Aus diesem Grund müssen sicherheitsrelevante ICs, wie Smart Power ICs, in der Gegenwart von zufälligen Hardwarefehlern einen sicheren Betriebszustand gewährleisten. Hierzu wird die Funktionalität des ICs durch diagnostische Funktionen und Sicherheitsmechanismen erweitert.

Halbleiterunternehmen haben dieses Thema unlängst mit der Einführung der ISO 26262 erschlossen. Der Standard adressiert die funktionale Sicherheit von Straßenfahrzeugen und widmet sich dabei insbesondere den elektrischen, elektronischen und programmierbar elektronischen Komponenten im System. Im Allgemeinen bietet der Standard ein Rahmenwerk an Anforderungen, das den gesamten Entwicklungsprozess sicherheitsrelevanter ICs betrifft. Halbleiterunternehmen stehen in diesem Kontext neuen Herausforderungen gegenüber.

Die funktionale Verifikation mithilfe computergestützter Entwurfsmethoden, engl. computer aided design (CAD), und Simulation, d.h. Pre-Silicon Verifikation, stellt eine entscheidende Phase innerhalb der IC-Entwicklung noch vor der Produktion von Prototypen dar. Dabei wird der Schaltungsentwurf auf Abweichungen von seinem vorgesehenen funktionalen Verhalten überprüft. In diesem Kontext fordert die ISO 26262 explizit die simulationsbasierte Injektion von Hardwarefehlern in den Schaltungsentwurf. Dies gilt der Evaluierung des Schaltungsentwurfs hinsichtlich seiner diagnostischen Kapabilität sowie Erfüllung von sicherheitsbezogenen funktionalen Anforderungen in der Gegenwart von Hardwarefehlern.

Die simulationsbasierte Fehlerinjektion für AMS ICs gilt bereits seit den frühen 90ern als eine herausfordernde Aufgabe. Dies ist hauptsächlich auf das Fehlen eines generell akzeptierten Maßes für die Fehlerabdeckung sowie die damit verbundenen Fehlermodelle zurückzuführen. Außerdem ist eine eingehende Fehlersimulation auf Transistor-Ebene (Netzliste) für große Schaltungsentwürfe aufgrund der Simulationsdauer nicht praktikabel. Zudem bietet derzeit kein kommerzielles CAD-Tool die automatisierte Fehlerinjektion für AMS ICs. Dadurch ist die Fehlerinjektion mit erheblichem manuellem Arbeitsaufwand verbunden. Es wird eine adequate Methodik benötigt, die

die genannten Herausforderungen berücksichtigt und entsprechende Lösungsansätze liefert, um die Pre-Silicon Verifikation im Kontext der funktionalen Sicherheit zu realisieren. Die vorliegende Arbeit widmet sich diesem Thema.

Zunächst wird ein Ansatz für die Integration und Automatisierung der Fehlerinjektion in dem kommerziellen CAD-Tool Cadence<sup>®</sup> Virtuoso<sup>®</sup> vorgeschlagen und implementiert. Hierzu wird eine Fehlermodellbibliothek entwickelt, mit der die Fehlerinjektion auf unterschiedlichen Abstraktionsebenen des Schaltungsentwurfs ermöglicht wird. Für die Strukturierung und Planung der Pre-Silicon Verifikation im Kontext der funktionalen Sicherheit wird initial eine Failure Modes, Effects and Diagnostic Analysis (FMEDA) verwendet. Danach wird ein Ansatz für hierarchische Fehlerinjektion vorgeschlagen, mit dem Zweck redundante Fehlersimulationen zu vermeiden und somit die Effizienz der Verifikation bei großen Schaltungsentwürfen zu erhöhen. Schließlich werden parametrische Soft-Fehler bei der Fehlerinjektion betra-Die Effekte der Soft-Fehler werden auf der Basis der Fehlerinjektion mit variabler Parametrierung durch eine qualitative und quantitative globale Sensibilitätsanalyse untersucht. Zu diesem Zweck werden aus den Simulationsergebnissen Sensibilitätsindizes berechnet, die jeweils den Beitrag eines Soft-Fehlers zur Varianz des Schaltungsausgangssignals quantifizieren. Die Sensibilitätsindizes werden verwendet um Soft-Fehler nach Wichtigkeit einzuorden sowie vernachlässigbare Soft-Fehler zu identifizieren.

Die experiementellen Ergebnisse werden anhand von zwei Modulen in sicherheitsrelevanten Applikationen aus dem Automobilbereich generiert. Dabei handelt es sich um ein Modul zum Ausgleich und zur Überwachung von Lithium-Ionen Zellen sowie einem Gate-Treibermodul, welches eine sicherheitsrelevante Funktion in einem System-on-Chip (SOC) durchführt. Abschließend wird die Arbeit zusammengefasst und ein Ausblick auf die zukünftige Entwicklung gegeben.

# Contents

|   | List | of Abbreviations                                                                                                            |   |   |   | • |   |   | xiii            |

|---|------|-----------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|-----------------|

| 1 | Intr | oduction                                                                                                                    |   |   |   |   |   |   | 1               |

|   | 1.1  | Background                                                                                                                  |   |   |   |   |   |   | 1               |

|   |      | 1.1.1 Automotive electronic control units                                                                                   |   |   |   |   |   |   | 1               |

|   |      | 1.1.2 Pre-silicon functional verification                                                                                   |   |   |   |   |   |   | 2               |

|   |      | 1.1.3 Failures in semiconductor devices                                                                                     |   |   |   |   |   |   | 6               |

|   |      | 1.1.4 Fault injection technique                                                                                             |   |   |   |   |   |   | 7               |

|   |      | 1.1.5 Concepts and definitions of the ISO 26262 .                                                                           |   |   |   |   |   |   | 9               |

|   | 1.2  | Motivation                                                                                                                  |   |   |   |   |   |   | 15              |

|   | 1.3  | Challenges                                                                                                                  |   |   |   |   |   |   | 15              |

|   | 1.4  | Scope of this thesis                                                                                                        |   |   |   |   |   |   | 16              |

|   | 1.5  | $Outline \dots \dots$ |   |   |   |   |   |   | 16              |

| 2 | Rela | ated work                                                                                                                   |   |   |   |   |   |   | 19              |

| _ | 2.1  | Computer-aided safety analysis                                                                                              |   |   |   |   |   |   | 19              |

|   |      | 2.1.1 High-level model-based approaches                                                                                     |   |   |   |   |   |   | 19              |

|   |      | 2.1.2 Low-level model-based approaches                                                                                      |   |   |   |   |   |   | 20              |

|   | 2.2  | Digital fault simulation                                                                                                    |   |   |   |   |   |   | 20              |

|   | 2.2  | 2.2.1 Fault collapsing                                                                                                      |   |   |   |   |   |   | 20              |

|   |      | 2.2.2 Digital fault modelling and injection                                                                                 |   |   |   |   |   |   | 21              |

|   |      | 2.2.3 Simulation speed-up                                                                                                   |   |   |   |   |   |   | 21              |

|   | 2.3  | Analog fault simulation                                                                                                     |   |   |   |   |   |   | 22              |

|   | 2.0  | 2.3.1 Analog fault classification                                                                                           |   |   |   |   |   |   |                 |

|   |      | 2.3.2 Model abstraction techniques                                                                                          |   |   |   |   |   |   | $\frac{22}{25}$ |

|   |      | 2.3.3 Analog functional fault equivalence                                                                                   |   |   |   |   |   |   |                 |

|   |      | 2.3.4 Simulator-dependent techniques                                                                                        |   |   |   |   |   |   |                 |

|   | 2.4  | Heterogeneous fault simulation                                                                                              |   |   |   |   |   |   |                 |

|   | 2.4  | Cummons                                                                                                                     | • | • | • | • | • | • | 21              |

| 3 | Dev | relopment of a fault simulation environment           | <b>29</b> |

|---|-----|-------------------------------------------------------|-----------|

|   | 3.1 | Elements of the fault simulation environment          | 29        |

|   | 3.2 | Circuit-level fault modelling                         | 30        |

|   | 3.3 | Functional fault modelling                            | 31        |

|   | 3.4 | Implementation of a fault model library               | 33        |

|   |     | 3.4.1 Electrical domain                               | 33        |

|   |     | 3.4.2 Fault injection in heterogeneous systems        | 38        |

|   |     | 3.4.3 Digital fault models                            | 38        |

|   | 3.5 | Automation concepts                                   | 38        |

|   |     | 3.5.1 Dynamic fault injection                         | 39        |

|   |     | 3.5.2 Implementation in a CAD tool                    | 41        |

|   | 3.6 | Summary                                               | 45        |

| 4 | Saf | ety-related functional verification                   | 47        |

| 4 | 4.1 | Scope within ISO 26262                                | 47        |

|   | 4.1 | Evaluation of effects of random hardware failures     | 48        |

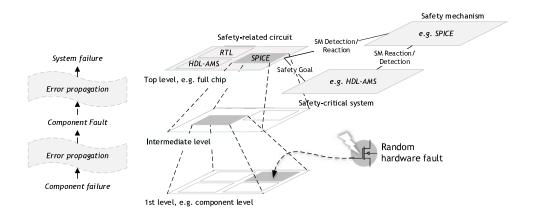

|   | 4.2 | 4.2.1 Generic architecture of a safety-related design | 48        |

|   |     | 4.2.2 Error propagation                               | 48        |

|   |     | 4.2.3 Realization of item-level fault simulations     | 49        |

|   | 4.3 | Verification plan                                     | 52        |

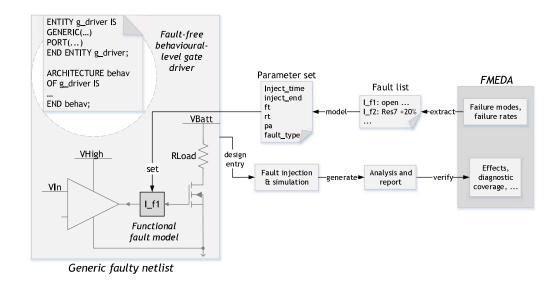

|   | 1.0 | 4.3.1 FMEDA-oriented approach                         | 52        |

|   |     | 4.3.2 Implementation of functional fault injection    | 52        |

|   | 4.4 | Summary                                               | 54        |

|   |     |                                                       |           |

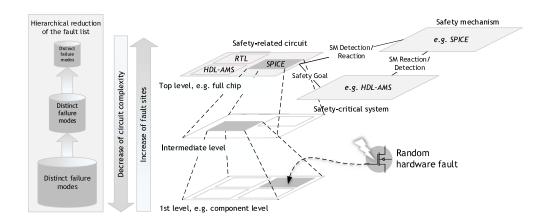

| 5 |     | lt grouping approach for hierarchical fault injection | 55        |

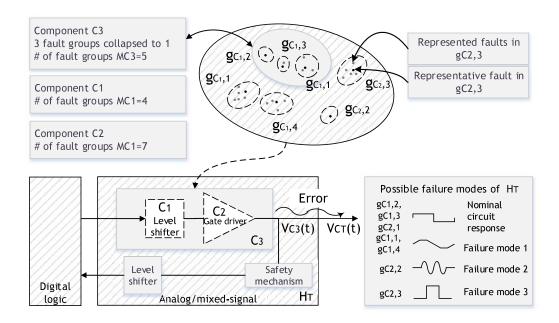

|   | 5.1 | Functional fault equivalence: a review                | 56        |

|   |     | 5.1.1 Hierarchical fault grouping                     | 56        |

|   |     | 5.1.2 Representative faults                           | 57        |

|   |     | 5.1.3 Functional fault collapsing rate                | 57        |

|   | 5.2 | Implementation overview                               | 58        |

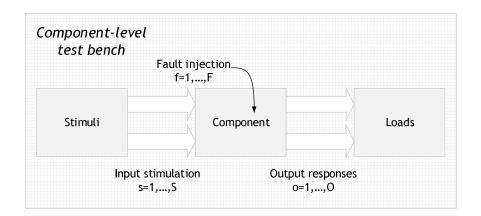

|   | 5.3 | Component-level simulation test bench                 | 59        |

|   | 5.4 | Hierarchical clustering algorithm                     | 60        |

|   |     | 5.4.1 Data set preparation                            | 61        |

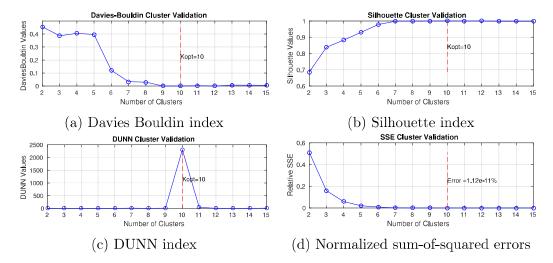

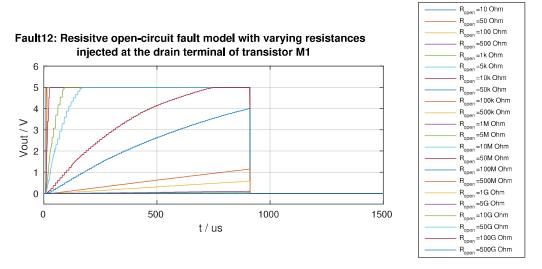

|   |     | 5.4.2 Optimal set of fault groups                     | 63        |

|   | 5.5 | Choice of representative faults                       | 65        |

|   |     | 5.5.1 Medoid criterion                                | 66        |

|   |     | 5.5.2 Worst-case criterion                            | 66        |

|   | 5.6 | Summary                                               | -66       |

| 6                | $\mathbf{Eva}$ | luation of soft faults by global sensitivity analysis                                                                                          | 67          |

|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                  | 6.1            | Modelling soft faults                                                                                                                          | 67          |

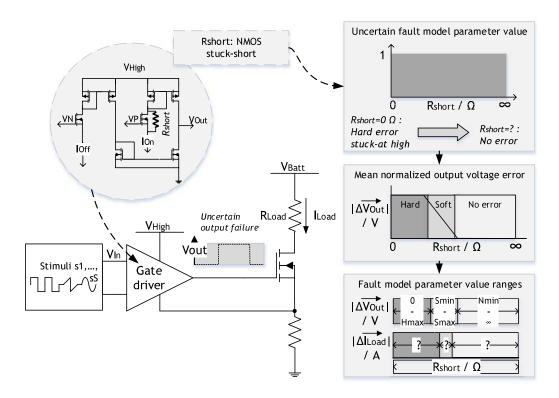

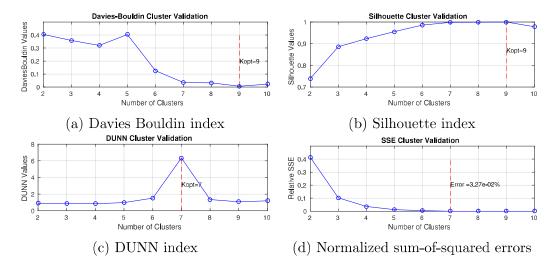

|                  | 6.2            | Component failure and fault model parameter ranges                                                                                             | 68          |

|                  |                | 6.2.1 Determination of soft failure ranges                                                                                                     | 69          |

|                  |                | 6.2.2 Mean normalized output error calculation                                                                                                 | 69          |

|                  | 6.3            | Global sensitivity analysis                                                                                                                    | 70          |

|                  |                | 6.3.1 Qualitative methods                                                                                                                      |             |

|                  |                | 6.3.2 Quantitative methods                                                                                                                     |             |

|                  | 6.4            | Evaluation of soft faults                                                                                                                      |             |

|                  |                | 6.4.1 Linear model assumption                                                                                                                  |             |

|                  |                | 6.4.2 Screening                                                                                                                                |             |

|                  |                | 6.4.3 Sampling-based effect estimates                                                                                                          |             |

|                  |                | 6.4.4 Sampling approach                                                                                                                        |             |

|                  | 6.5            | Summary                                                                                                                                        | 78          |

| 7                | Exp            | perimental results                                                                                                                             | <b>7</b> 9  |

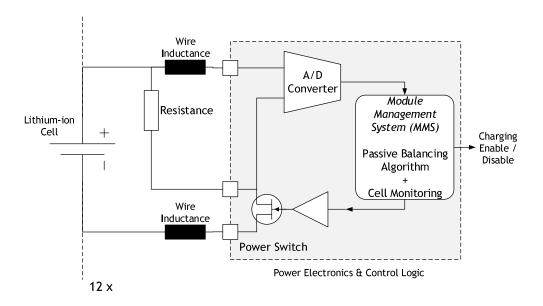

|                  | 7.1            | Battery management system module                                                                                                               | 79          |

|                  |                | 7.1.1 Passive balancing of Lithium-ion cells                                                                                                   | 79          |

|                  |                | 7.1.2 Elements and functionality                                                                                                               | 80          |

|                  |                | 7.1.3 Case study: Evaluation of safety goal violations                                                                                         | 81          |

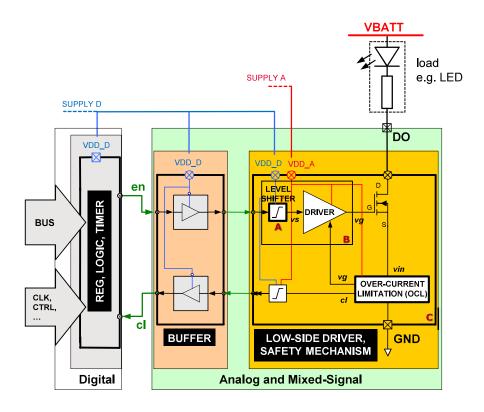

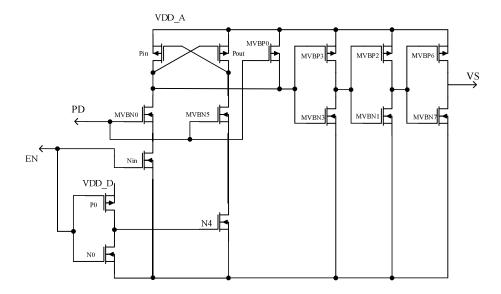

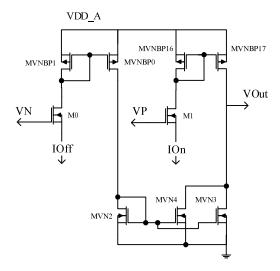

|                  | 7.2            | Low-side gate driver circuit                                                                                                                   | 91          |

|                  |                | 7.2.1 Elements                                                                                                                                 | 91          |

|                  |                | 7.2.2 Functionality                                                                                                                            | 91          |

|                  |                | 7.2.3 Case study: Safety-related functional verification                                                                                       | 93          |

|                  |                | 7.2.4 Case study: Hierarchical fault injection                                                                                                 |             |

|                  |                | 7.2.5 Case study: Evaluation of soft structural faults                                                                                         | 107         |

| 8                | Cor            | nclusion and outlook                                                                                                                           | 117         |

|                  | 8.1            | Conclusion                                                                                                                                     | 117         |

|                  | 8.2            | Future work                                                                                                                                    | 119         |

| Pι               | ıblic          | ations                                                                                                                                         | 121         |

| $\mathbf{A}_{]}$ |                | ${ m dix}{ m A}{ m Algorithms}{ m for}{ m fault}{ m injection}{ m automation}{ m g}{ m the}{ m Cadence}^{ m I\!B}{ m OpenAccess}{ m database}$ | 123         |

| $\mathbf{A}_{]}$ | ppen           | dix B Algorithms for hierarchical fault injection                                                                                              | <b>12</b> 9 |

| $\mathbf{A}_{]}$ | ppen           | dix C Algorithms for the evaluation of soft faults                                                                                             | 133         |

| Bi               | blios          | graphy                                                                                                                                         | 135         |

# List of Abbreviations

| ASIL                 | Automotive Safety Integrity Level                   |

|----------------------|-----------------------------------------------------|

| CAD                  | Computer-Aided Design                               |

| DC                   | Diagnostic Coverage                                 |

| DPF                  | Dual-Point Fault                                    |

| E/E/PE               | Electrical/Electronic/Programmable Electronic       |

| ECU                  | Electronic Control Unit                             |

| $\operatorname{FET}$ | Field Effect Transistor                             |

| FMEA                 | Failure Mode and Effect Analysis                    |

| FMEDA                | Failure Mode, Effect and Diagnostics Analysis       |

| FPGA                 | Field Programmable Gate Array                       |

| FSR                  | Functional Safety Requirements                      |

| $\mathrm{HDL}$       | Hardware Description Language                       |

| HSR                  | Hardware Safety Requirements                        |

| MEMS                 | Micro-Electromechanical System                      |

| MPF,D                | Multiple-Point Fault, Detected                      |

| $_{\mathrm{MPF,L}}$  | Multiple-Point Fault, Latent                        |

| $_{\mathrm{MPF,P}}$  | Multiple-Point Fault, Perceived                     |

| PDF                  | Probability Density Function                        |

| RF                   | Residual Fault                                      |

| RHF                  | Random Hardware Failure                             |

| RTL                  | Register Transfer Level                             |

| $\operatorname{SF}$  | Safe Fault                                          |

| $\operatorname{SG}$  | Safety Goal                                         |

| $\operatorname{SIL}$ | Safety Integrity Level                              |

| SM                   | Safety Mechanism                                    |

| $\operatorname{SoC}$ | System-on-Chip                                      |

| SPF                  | Single Point Fault                                  |

| SPICE                | Simulation Program with Integrated Circuit Emphasis |

| TSR                  | Technical Safety Requirements                       |

| UML                  | Unified Modelling Language                          |

# List of Figures

| 1.1 | Example of an ECU with smart power devices and peripheral             | า  |

|-----|-----------------------------------------------------------------------|----|

| 1.0 | devices [1]                                                           | 3  |

| 1.2 | Top-down abstraction models [2]                                       | 4  |

| 1.3 | Self-checking test bench [2]                                          | 5  |

| 1.4 | Bathtub curve function for semiconductor failure rate calculation [2] | 6  |

| 1.5 | lation [3]                                                            | 10 |

|     | ·                                                                     |    |

| 1.6 | Classification of system failures                                     | 11 |

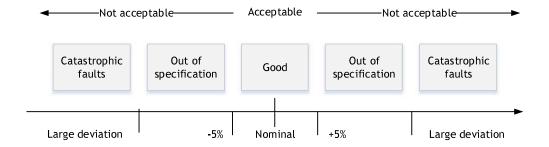

| 2.1 | Classification of analog circuit faults with $\pm 5\%$ tolerance for  |    |

|     | deviation from nominal [5]                                            | 22 |

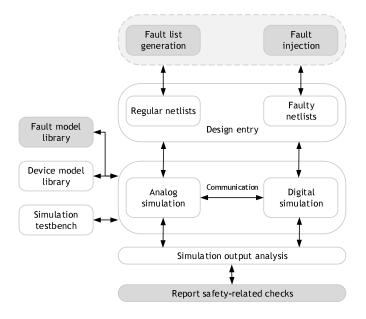

| 3.1 | Elements of the mixed-signal simulation environment with in-          |    |

|     | tegrated facility for fault injection                                 | 30 |

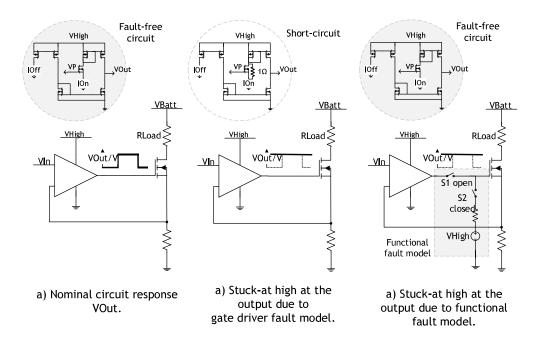

| 3.2 | Circuit-level and functional fault modelling on a low-side gate-      |    |

|     | driver example                                                        | 32 |

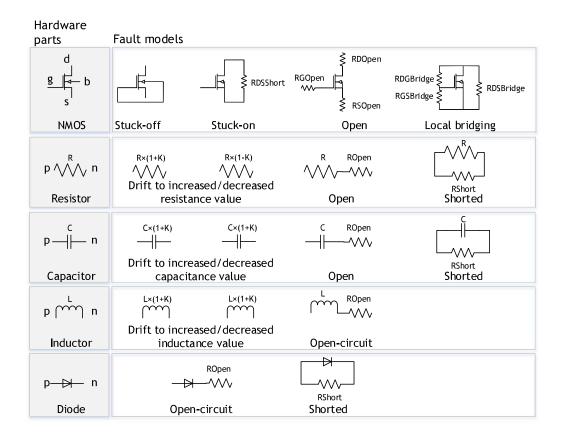

| 3.3 | Some types of hardware parts and fault models                         | 34 |

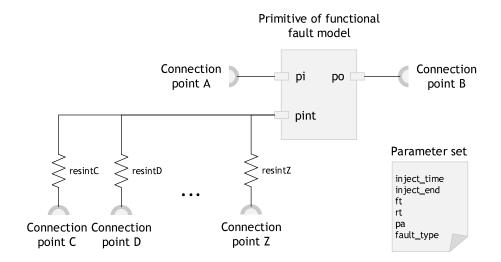

| 3.4 | Basic schematic of the functional fault model                         | 35 |

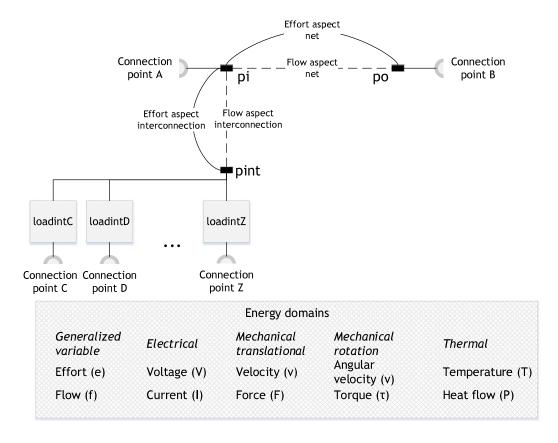

| 3.5 | Domain-independent architecture of the functional fault model.        | 39 |

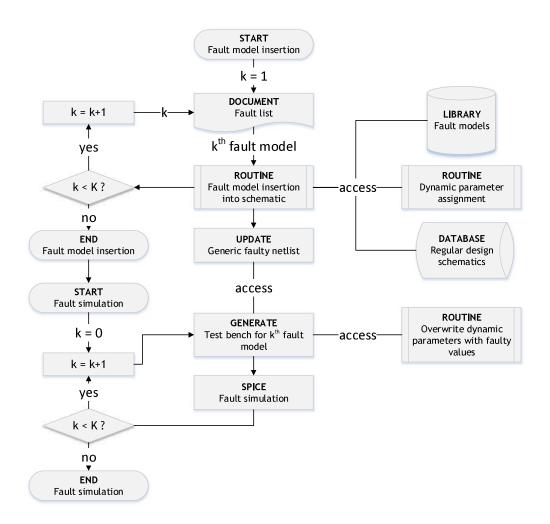

| 3.6 | Flow diagram of the automation concept for dynamic fault              |    |

|     | injection                                                             | 40 |

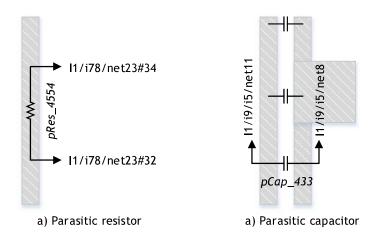

| 3.7 | Example of layout extracted parasitic resistance and capaci-          |    |

|     | tance                                                                 | 43 |

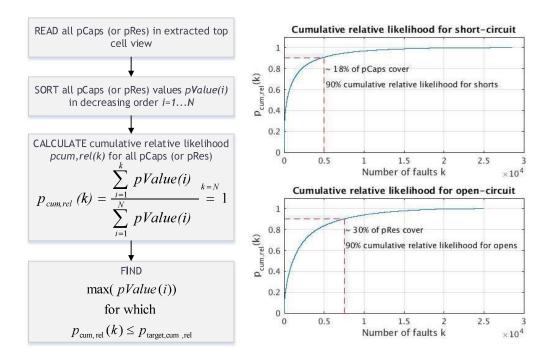

| 3.8 | Algorithm for determining the parasitic threshold values              | 43 |

| 4.1 | Error propagation of a random hardware fault to a top level           |    |

|     | failure in a safety-related circuit with hierarchical architecture.   | 49 |

| 4.2 | Simplified extract of an FMEDA                                        | 52 |

| 4.3 | Implementation of the FMEDA-oriented simulation-based safety          |    |

|     | analysis                                                              | 53 |

| 5.1 | The number of distinguishable failure modes decreases with increasing level of design hierarchy due to functional fault equiv-                                                                                                                        | <b>.</b>                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.2 | alence                                                                                                                                                                                                                                                | 56                              |

| 5.3 | in analog and mixed-signal circuits                                                                                                                                                                                                                   | <ul><li>58</li><li>60</li></ul> |

| 6.1 | Component failure with respect to a resistive short-circuit fault model                                                                                                                                                                               | 68                              |

| 7.1 | Simplified schematic of the battery management module with passive balancing function                                                                                                                                                                 | 80                              |

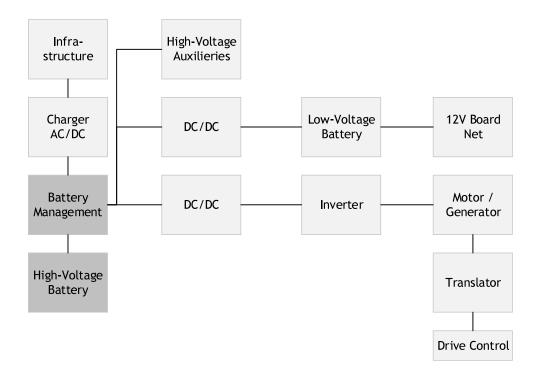

| 7.2 | Electric drive train as item with corresponding hardware elements                                                                                                                                                                                     | 82                              |

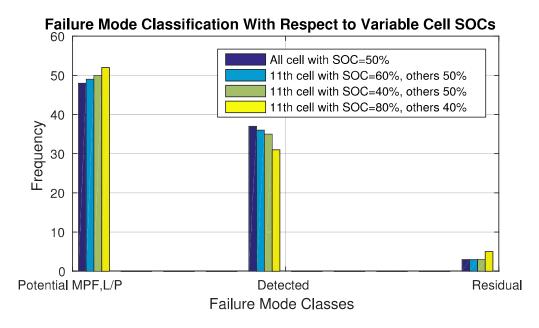

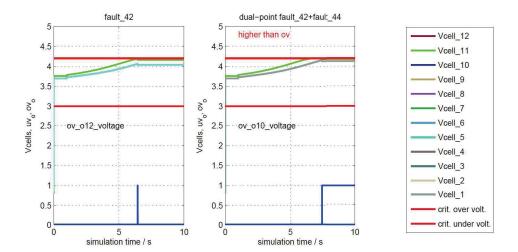

| 7.3 | Failure mode classification results for single-point fault injection and variable cell SOCs                                                                                                                                                           | 86                              |

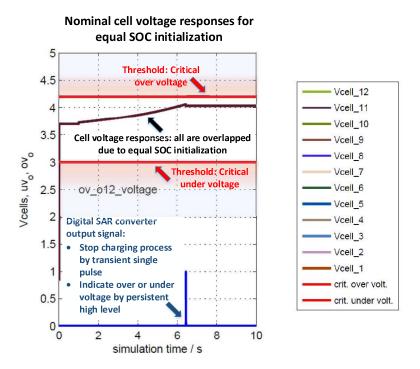

| 7.4 | Simulation results for the nominal cell voltage response with all cells initialised to equal SOC=50%. Cell voltages, critical over- and under-voltages are drawn together with the digital                                                            | 00                              |

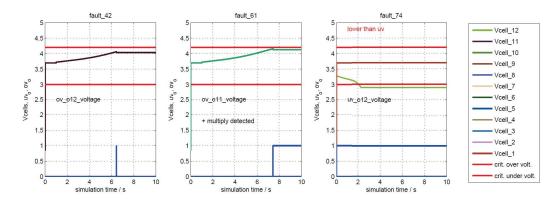

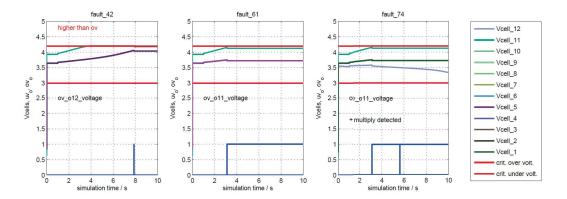

| 7.5 | over-voltage and under-voltage detection                                                                                                                                                                                                              | 88                              |

| 7.6 | voltage and under-voltage detection                                                                                                                                                                                                                   | 89                              |

| 7.7 | gether with the digital over-voltage and under-voltage detection. Comparison of single-point and dual-point fault injection. The 11th cell is initialised to SOC=60% and all other cells to SOC=50%. Cell voltages, critical over- and under-voltages | 89                              |

| 7.8 | are drawn together with the digital over-voltage and under-voltage detection                                                                                                                                                                          | 90                              |

|     | current limitation circuit (OC)                                                                                                                                                                                                                       | 92                              |

| 7.9  | Circuit of the active-high level shifter shifter (LS) which lifts the input signal $en$ from the digital level $VDD_{\rm D}$ into the analog level $VDD_{\rm A}$ , resulting in the output signal $vs$ . The second                                                |          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | input signal $pd$ indicates a power supply failure in the digital control unit and disables the output signal $vs.$                                                                                                                                                | 93       |

| 7.10 | Circuit of the low-side gate driver output stage (OS). The gate driver signal $v_{\text{Out}}$ is driven by input signals $V_N$ and $V_P$ . The output slew rate is controlled via $I_{Off}$ and $I_{On}$ , provided by                                            | 0.4      |

| 7.11 | bias circuitry (not shown)                                                                                                                                                                                                                                         | 94       |

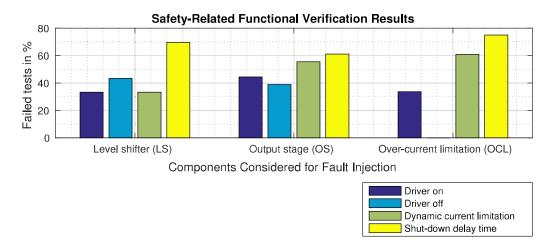

| 7.12 | ferent test cases                                                                                                                                                                                                                                                  | 96<br>97 |

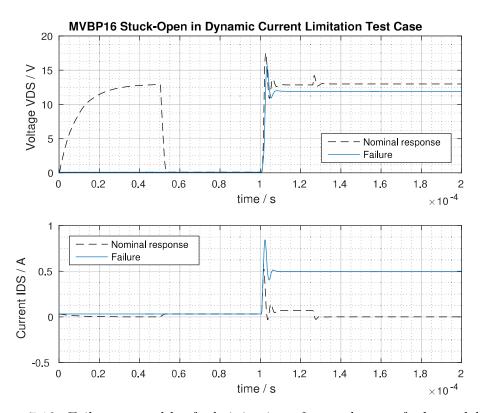

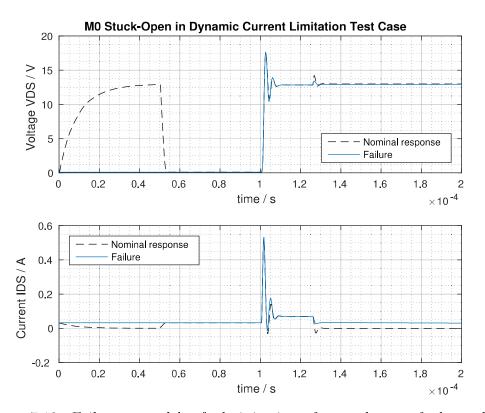

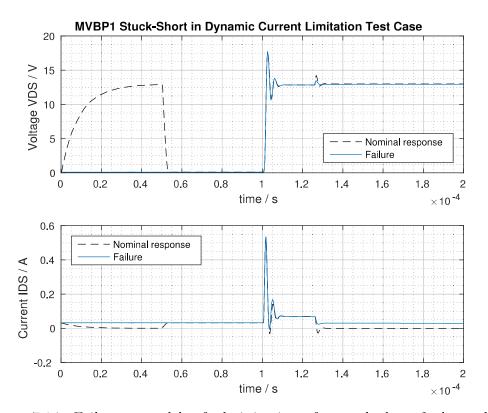

| 7.13 | Failure caused by fault injection of a stuck-open fault model of NMOS M0 in the gate driver output stage. Simulated waveforms of the Power MOSFET voltage $VDS$ and current $IDS$ in nominal and failure mode during the dynamic current limitation test case      | 98       |

| 7.14 | Failure caused by fault injection of a stuck-short fault model of PMOS MVBP1 in the gate driver output stage. Simulated waveforms of the Power MOSFET voltage $VDS$ and current $IDS$ in nominal and failure mode during the dynamic current limitation test case. | 99       |

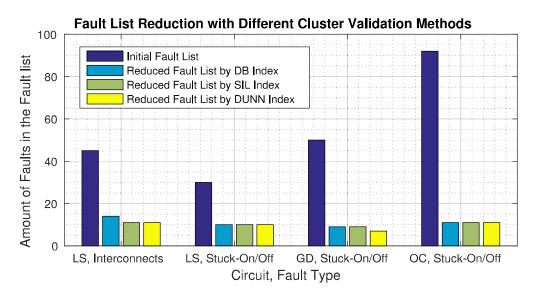

| 7.15 | Interconnect and stuck-open/short fault grouping results for the level-shifter circuit (LS), gate driver circuit (GD) and over-current limitation circuit (OC).                                                                                                    |          |

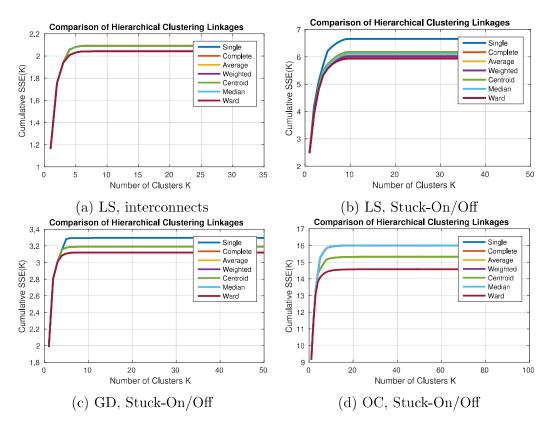

| 7.16 | Comparison of the cumulative sum-of-squared errors using different linkage functions in the hierarchical clustering algorithm.                                                                                                                                     |          |

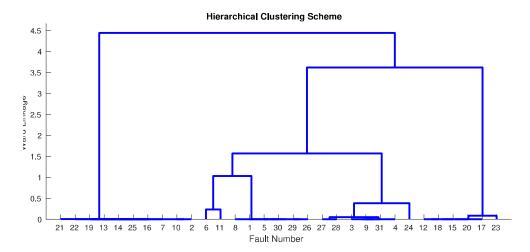

| 7.17 | Hierarchical clustering scheme (dendrogram) of stuck-open/-short faults for the level shifter with enumerated faults (1 is the nominal circuit response)                                                                                                           |          |

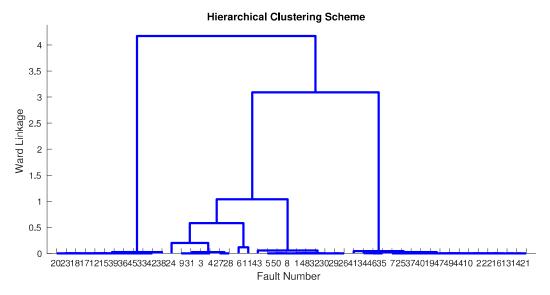

| 7.18 | Hierarchical clustering scheme (dendrogram) of stuck-open/-                                                           |

|------|-----------------------------------------------------------------------------------------------------------------------|

|      | short faults in the output stage with the level shifter as sub-                                                       |

|      | component. The level shifter faults are enumerated from 1 to                                                          |

|      | 31, the output stage faults are enumerated from 32 to 50 (1                                                           |

|      | and 32 are nominal circuit responses) 103                                                                             |

| 7.19 | Cluster validation results for stuck-open/-short faults in the                                                        |

|      | level shifter                                                                                                         |

| 7.20 | Cluster validation results for stuck-open/-short faults in the output stage (with level shifter as sub-component) 106 |

| 7.21 | - · · · · · · · · · · · · · · · · · · ·                                                                               |

| 1.21 | Resistance ranges for hard, soft and nominal stuck-open/-short faults in the output stage                             |

| 7 22 | Circuit responses of the gate driver output-stage to soft stuck-                                                      |

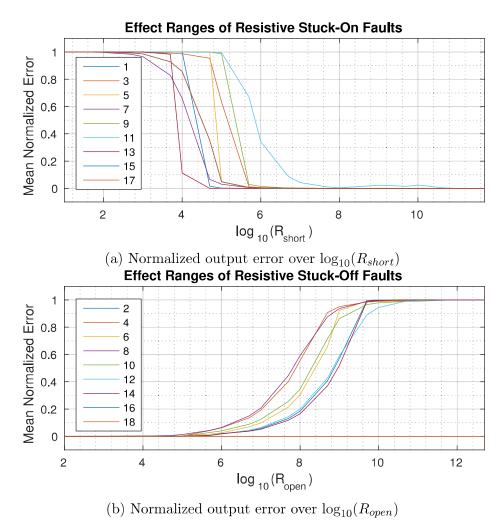

| 1.22 | open fault model of transistor M1                                                                                     |

| 7.23 | Circuit responses of the gate driver output-stage to soft stuck-                                                      |

|      | short (uneven numbers) and stuck-open (even numbers) fault                                                            |

|      | injection. Faults 16 and 18 have only an effect when occurring                                                        |

|      | simultaneously                                                                                                        |

| 7.24 | Screening results for soft stuck-short and stuck-short faults.                                                        |

|      | The total effects are read on the horizontal axis in increasing                                                       |

|      | order                                                                                                                 |

| 7.25 | Direct and total effects and contributions of soft stuck-short                                                        |

|      | faults to the model $R^2$                                                                                             |

| 7.26 | Direct and total effects and contributions of soft stuck-open                                                         |

|      | faults to the model $R^2$                                                                                             |

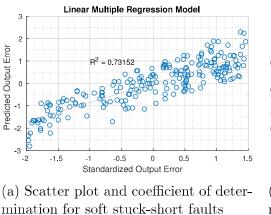

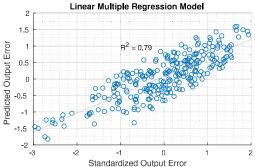

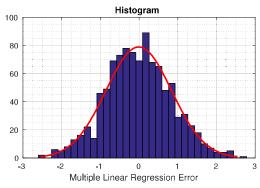

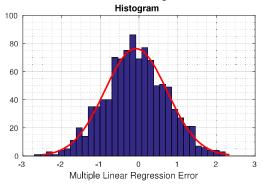

| 7.27 | Validation of the linear regression model: coefficient of determination and regression errors                         |

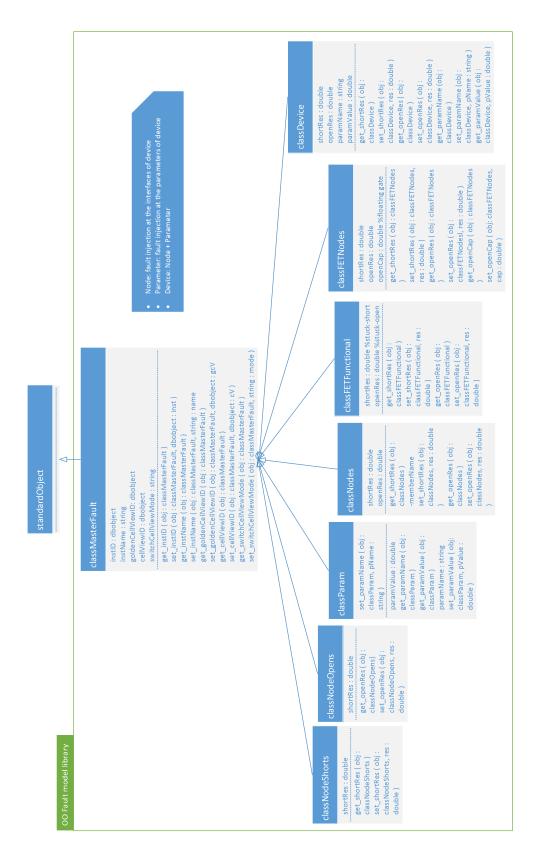

| A.1  | UML class diagram of the object-oriented fault model library. 128                                                     |

# List of Tables

| 1.1<br>1.2<br>1.3                 | Qualitative comparison of advantages (+) and disadvantages (-) of different methods to conduct the fault injection Possible target random hardware failure rates [4] Possible target hardware architectural metrics [4]               | 8<br>13<br>14 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 3.1<br>3.2                        | Default set of faults covered by the fault insertion algorithm                                                                                                                                                                        | 35<br>42      |

| 4.1                               | Examples of fault, error and failure relation in electrical, mechanical and thermal domain which can be represented with a functional fault model                                                                                     | 51            |

| 5.1                               | 1                                                                                                                                                                                                                                     | 60            |

| <ul><li>5.2</li><li>5.3</li></ul> | Cluster validation methods [7, 8, 9] used for the determination                                                                                                                                                                       | 64<br>65      |

| 7.1                               | 1 0 1                                                                                                                                                                                                                                 | 83            |

| <ul><li>7.2</li><li>7.3</li></ul> | Results for $K_{\text{opt}} = 10$ optimal fault groups in the level shifter component: devices, enumerated stuck-open/-short faults, fault group assignments and arguments for medoid and worst-case representative fault calculation |               |

| 7.4                               | Stuck-open/short fault list for soft fault injection with resistive fault models in the output stage of the low-side gate driver module                                                                                               |               |

# Chapter 1

# Introduction

Safety-related functions in road vehicles are more and more implemented by electronic control units (ECUs). Modern automotive ECUs are highly-integrated, multi-functional integrated circuits (ICs), processing digital as well as analog (mixed) signals. With increasing automotive electrification and functional complexity, the risk from random hardware failures increases. The evaluation of the circuit's functional performance in the presence of a random hardware failures thereby plays a crucial role. Recently, this topic came to the spotlight in the semiconductor industry due to the functional safety standard for road vehicles, ISO 26262.

This thesis addresses the topic safety-related pre-silicon functional verification of automotive ECUs with emphasis on the analog/mixed-signal domain. This chapter provides a background on fundamental concepts related to this topic and the motivation for this work. Subsequently, the challenges regarding the addressed topic are explained and the scope of this thesis is defined. Finally, an outline for the thesis is provided.

# 1.1 Background

In this section, the background on automotive ECUs, failures in semiconductor devices, pre-silicon functional verification as well as concepts and definitions in the ISO 26262 is provided.

#### 1.1.1 Automotive electronic control units

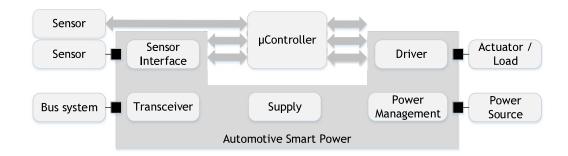

Automotive ECUs comprise smart power devices [10]. Smart power devices are semiconductor devices which integrate power semiconductors [11] and peripheral circuitry to interface the digital control logic, loads and sensors

into a single unit. Additionally, they integrate self-diagnosis and peripheral protection circuits against for example current, voltage, temperature and electrostatic discharge surges [10]. Due to its advanced capability for large-scale integration and low energy consumption, the metal-oxide semiconductor (MOS) technology is predominantly used in smart power devices [10]. Fig. 1.1 shows a simplified example of an automotive ECU. Smart power devices can be distinguished with respect to their functionality in the application into [10, 1]:

- **Driver** The driver functionality is implemented by analog/mixed-signal circuits to drive several types of power actuators, for example LED modules, various types of electric motors or squibs.

- Supply The supply functionality maintains the voltage and current supply to other devices. Depending on the application, examples of supply circuits are bias circuits, linear voltage regulators and DC/DC converters.

- Transceiver this device facilitates the communication between different ECUs via various types of bus systems, for example CAN, LIN and FlexRay. Transceiver circuits convert the transmitted (received/sent) information for/from the ECU's embedded microcontroller.

- Power management This device is implemented by analog/mixedsignal circuits. Examples are battery management ICs, dedicated to monitor and balance Lithium-ion battery cells in electric vehicles and alternator control ICs, dedicated to stabilizing the vehicle's supply voltage.

- Sensor interface This device facilitates information transfer from the sensors to the ECU's embedded microcontroller.

## 1.1.2 Pre-silicon functional verification

The purpose of functional verification of an IC design is "to ensure that the design meets the functional requirements as defined in the functional specification" [2]. With increasing complexity and functional diversification of ICs ("More than Moore"), functional verification is getting even more challenging [12, 13]. This becomes evident when up to 70% of project resources are spent on functional verification during IC development [14]. Functional verification is generally distinguished into pre-silicon and post-silicon verification [15]. For post-silicon verification, a prototype of the actual hardware

Figure 1.1: Example of an ECU with smart power devices and peripheral devices [1].

is verified in a test environment. Pre-silicon verification on the other hand is undertaken before any silicon prototype is available. For this purpose, a model of the IC is verified at various abstraction levels using formal-based [16] and/or simulation-based methods [2]. Simulation-based verification is predominantly used in the industry due to its advantages in scalability compared to formal verification [17, 18].

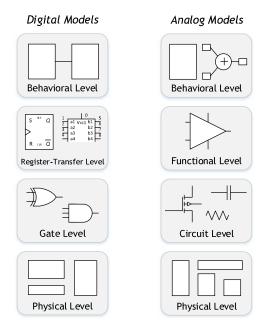

#### Model abstraction levels

For pre-silicon verification, the IC is typically modelled at different abstraction levels: architectural, behavioural, register-transfer level (RTL), gate level and circuit level (also transistor level or primitive level) [19]. The top-down design methodology starts with an abstract description of the circuit design and iteratively adds detail to the model [2], see fig. 1.2. The final level of lowest abstraction is the physical design (layout). Additionally, the gate-level/primitive-level netlist can be distinguished into pre-layout and post-layout netlist. Latter incorporates layout-specific parasitic resistive and capacitive elements.

Due to digital synthesis [20] (automatic translation of an abstract model, typically RTL, into the logic-gate level design), the digital design implementation methodology diverges substantially from that of the analog design implementation [19]. Contrary, analog/mixed-signal design implementation at transistor level is done manually by means of electronic computer-aided design (CAD) software tools [21].

Figure 1.2: Top-down abstraction models [2].

#### Mixed-signal verification methodology

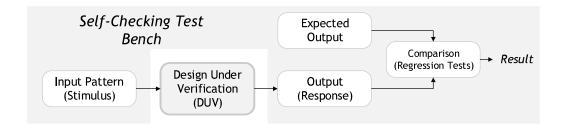

Simulation-based verification methodologies diverge strongly for the digital and analog parts in mixed-signal circuits. For digital circuits, typically the RTL model is used to represent the design under verification (DUV) in a simulation test bench. The verification thoroughness is expressed in terms of coverage metrics: code coverage [22], assertion coverage [23] and functional coverage [24]. They quantify how well the circuit's functionalities are exercised for a given set of input signal pattern (stimuli). Stimuli are developed in a directed (user-defined) fashion or in a randomized fashion by including constraints to the multi-dimensional input space ("Constrained-Random Stimuli)" [25].

#### Analog verification methodology

For analog/mixed-signal circuits, the constrained-random and coverage-driven verification methodology is a topic of recent research and still under development [26]. This is mainly due to two reasons: the ambiguity in defining analog coverage metrics [27, 28, 29] and the lack of a correct-by-construction abstract model of the analog circuit, analogous to the RTL model in the dig-

Figure 1.3: Self-checking test bench [2].

ital domain [30]. Additionally, transient simulation time is a major concern for complex circuits at the transistor level.

The computational burden of circuit-level simulation is addressed by analog or real-number behavioural modelling using hardware description languages (HDL) [31], like for example VHDL/-AMS [32, 33] and Verilog/-AMS [34, 35]. However, the models are not correct-by-construction, i.e. subsequent equivalence checks between the abstract model and the transistor-level model are necessary [18]. The accuracy of the behavioural model depends on its level of detail. For example, a highly detailed behavioural model can take even more simulation time as its circuit-level equivalent [36].

For complex circuits this is addressed by hierarchical verification [30] and mixed-mode/mixed-level simulations [37, 38]. To attain consistency throughout the design hierarchy, the verification typically starts by component-level verification with circuit-level DUV verified against the component-level design specification. Subsequently, the verified components are used in the top-level (or intermittent design level) test bench. For top-level verification, mixed-mode (combination of circuit-level and RTL) and mixed-level (combination of circuit-level and behavioural model) simulations are considered [37, 38]. For example, critical circuits which are in focus of verification are kept at circuit level and non-critical circuits, like bias generators and digital parts are modelled in HDL, respectively [30].

The test bench for the analog/mixed-signal DUV is typically constructed as code or as a schematic in a CAD software tool, see fig. 1.3 [2]. The test bench comprises stimuli defining input pattern for which the DUV is exercised for different operating modes. In a self-checking test bench the DUV output is compared with the expected output by regression testing [2].

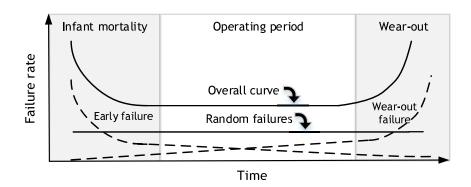

Figure 1.4: Bathtub curve function for semiconductor failure rate calculation [3].

## Analog verification flow

The analog verification flow starts with the design documentation from which design specification is extracted and design risks are identified. A verification plan is developed to cover the design requirements with the purpose of risk mitigation. The verification plan is implemented by the modelling plan and simulation plan for the component-level and top-level models. At the top level, a self-checking test bench is developed based on the verification plan, which can be configured regarding the component models to use for each test case (circuit level or behavioural/RTL level). The final design and layout is obtained in an iterative process when all regression tests pass. This means that the design implementation is conform with the design specification.

## 1.1.3 Failures in semiconductor devices

For semiconductor devices, three failure regions are distinguished: early failure, random failure and wear-out failure [39]. The failure rate calculation is based on the bathtub curve function, see fig. 1.4 [40]. In this model, the early failure rate decreases steadily over time, the random failure rate is a constant value and the wear-out failure rate decreases steadily. At each point in time, the bathtub-shaped curve is the sum of the three failure rates.

#### Random failures

Between the early failure period and wear-out, the device may be subject to random failures during field operation. The failure rate  $\lambda$  of random failures is a constant and much lower than the early or wear-out failure rates. Random failures and failure rates are determined by operating life tests in dynamic electric operation. The failure rate is generally calculated by [3]

$$\lambda = \frac{\text{Sum of failures}}{\sum (\text{Quantity} \times \text{Time to failures})}.$$

(1.1)

The failure in time (FIT) rate is another common notation, with one FIT being equal to  $\lambda = 10^9 \frac{1}{h}$  failures per device hours. Besides operating life tests, reliability handbooks are used to obtain the information on failure rates and generic random failures for different devices, that is failure modes [39]. Additionally, frequent causes for transient random failures are  $\alpha$ -particles and cosmic radiation [41], electromagnetic interference (EMI) [42] and crosstalk [43], as well as electrostatic discharge [10].

### Safety analysis

Safety analysis is performed with the purpose to evaluate and mitigate the risk of hazardous events due to random failures. The Failure Mode and Effect Analysis (FMEA) [44] and Fault Tree Analysis (FTA) [45] are commonly used safety analysis methods in the automotive and electronics industry. Both, FMEA and FTA consider the possible failures which may occur in the system and their effects. The FMEA is based on an inductive approach, inferring consequences (effects) from causes (failure). The FTA on the other hand, deductively infers from consequences to possible causes.

The FMEA was developed [44] and standardized [46] by the U.S. military to study the problems arising from malfunctioning military systems. However the tool was further developed by aerospace and automotive industries to fit in to the respective field. The Failure Modes, Effects and Diagnostic Analysis (FMEDA) is an extension of FMEA for safety-related systems and additionally includes information on quantitative failure rates, failure mode distributions and diagnostic capability of the respective failure detection and prevention measures in a system.

## 1.1.4 Fault injection technique

From a general point of view, the fault injection technique [47] is used to evaluate the performance of a system in the presence of a fault (e.g. in terms

| Fault injection into | Circuit representation | Fault coverage | Effort |

|----------------------|------------------------|----------------|--------|

| Hardware             | +                      | -              | -      |

| Emulation            | +                      | 0              | -      |

| Simulation           | 0                      | +              | +      |

| Formal model         | -                      | 0              |        |

Table 1.1: Qualitative comparison of advantages (+) and disadvantages (-) of different methods to conduct the fault injection.

of diagnostic capability) [48] and cause-consequence relationships between faults and their effects [49]. Fault injection technique is reportedly conducted hardware-based [50, 51], emulation-based [52, 53, 53], simulation-based [54, 55, 56] and formal-model-based [57, 58], see tab. 1.1. In the following, they are evaluated respective to their capabilities in circuit representation, fault coverage and effort for fault modelling and injection. Fault coverage refers to the capability to address any desired device or node in the circuit for fault injection.

While by hardware-based fault injection obviously a very high circuit representation is obtained, a limited number of nodes can be addressed for fault injection, thus a low fault coverage. Additionally, high effort is required to conduct the fault injection campaigns (e.g. Design-for-Test [59]). Only externally caused faults at primary input and output ports can be injected as well as at test ports, designed for this purpose.

In the emulation-based fault injection, the circuit RTL code including the fault models are first synthesized on a Field Programmable Gate Array (FPGA). With this technique, the performance of the circuit can be evaluated in real-time [60]. However, it is associated with high effort to conduct a fault injection campaign and is limited to digital circuits only. Additionally, the correlation between gate-level and RTL fault models is limited to stuck-at faults but not for example for bridging faults [61].

Simulation-based fault injection incorporates a circuit netlist as a model and a Simulation Program with Integrated Circuit Emphasis (SPICE) simulator [62]. This technique offers a variety of abstraction capabilities of the circuit for the benefit of lower simulation time. The fault coverage is very high as any node and device in the netlist can be addressed for fault injection. Compared to the other approaches, low effort for fault injection is required. However, the main disadvantage of simulation-based fault injection is that it is computation intensive.

For the formal-model-based fault injection, first a model of the circuit and

fault models are developed which are described in a formal language. This is generally associated with modelling effort. Moreover, large-scale complex circuits and analog circuits boost up the formal model and make it intractable and impractical for use for fault injection [58].

## 1.1.5 Concepts and definitions of the ISO 26262

The compliance of a product with the functional safety standard for road vehicles, ISO 26262, is determined for items of the vehicle. Items are defined to implement safety-related functions at the vehicle level and can be regarded as isolated from the rest of the vehicle. The standard [4] provides further concepts and definitions which are described in the remainder.

### Hardware design

The item is divided into different element types based on the level of detail: (sub-)systems, components, hardware parts and software units. Moreover, it is generally comprised of at least one system which is composed of at least one sensor, one controller and one actuator. Each of them is called a component. Components are composed of at least one hardware part (HW-part) or software unit (SW-Unit). In addition, elements comprised of lower-level HW-parts from electrical/electronic technology are also called components.

#### Fault, error, failure relationship

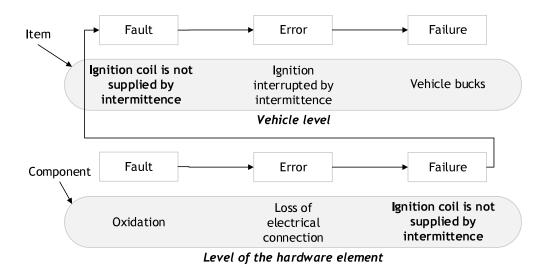

Faults are physically present in the hardware and cause an error which may propagate to a failure at the item level. A failure at the level of a hardware element is a hardware element fault at the item level, see fig. 1.5. An error is the deviation of a function implemented by a hardware element from its nominal function. A failure is the malfunctioning behaviour of a hardware element and a failure mode defines the manner in which a hardware element fails

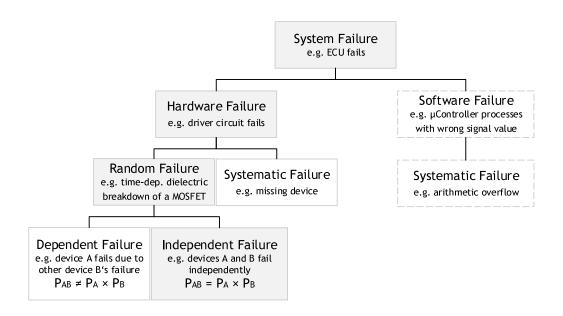

Based on random causes or systematic causes, failures in the hardware are distinguished into random hardware failures (RHFs) and systematic hardware failures, see fig. 1.6. Latter are due to deterministic issues in the hardware and can only be eliminated by re-design or change of the respective issues. RHFs on the other hand are due to physical processes including wearout, environmental stress and physical degradation. Moreover, the standard addresses independent random hardware failures. That is, the probability of occurrence of two independent failures  $P_{AB}$  is the product of each single

Figure 1.5: Faults, errors and failures in the hardware design [4].

failure probability  $P_A$  and  $P_B$ . Random hardware failures may occur unpredictably during application with a non-zero failure rate and are assumed to follow the exponential distribution

$$F(x) = \int_{-\infty}^{x} f_{\lambda}(t) dt = \begin{cases} 1 - e^{-\lambda x}, & \text{if } x \ge 0 \\ 0, & \text{if } x < 0 \end{cases}.$$

(1.2)

#### Types of safety requirements

In the concept phase of the safety life-cycle, possible hazardous events due to a RHF at the vehicle level are identified by a Hazard and Operability Analysis (HAZOP) and respective safety goals (SGs) are formulated. Thereby, hazardous events are assessed based on their severity, probability of exposure and controllability. Finally, an Automotive Safety Integrity Level (ASIL) for the avoidance of the hazardous event is derived which is based on this assessment and assigned to the respective SG. An example of a SG formulation is "Avoid deep discharge of any battery cell, ASIL D". In this example, the violation of the SG may cause the corresponding hazardous event "deep discharge of any battery cell" to occur. This occurrence must be prevented by utilizing prevention measures required to achieve ASIL D. Thus, SGs are top-level requirements which are assigned to the item.

Figure 1.6: Classification of system failures.

At a lower level of the hardware design, functional safety requirements (FSRs) are assigned to the elements in the hardware architecture. Compliance with FSRs is necessary to achieve the SGs. FSRs are independent from the hardware detailed design and implementation and are thus formulated at an early stage of the safety life-cycle.

At the level of the hardware detailed design, technical safety requirements (TSRs) are derived to implement the FSRs. TSRs comprise requirements for hardware as well as software. The hardware-related requirements of the TSRs are isolated from the software-related requirements in the hardware safety requirements (HSR). HSR are formulated with respect to the hardware implementation.

#### Failure mode classification

Failure modes are classified based on their potential to violate safety goals at the item level and their detectability by safety mechanisms. The classes are:

• Single-point fault (SPF) Causes a safety goal violation if no safety mechanism is implemented in the item.

- Residual fault (RF) Causes a safety goal violation in the presence of a safety mechanism which does not detect or control it.

- Multiple-point fault, latent (MPF,L) Singly not detected or perceived but violates a safety goal in combination with another fault.

- Multiple-point fault, detected (MPF,D) Singly detected but violates a safety goal in combination with another fault.

- Multiple-point fault, perceived (MPF,P) Singly perceived but violates a safety goal in combination with another fault.

- Safe fault (SF) Cannot cause singly or in combination with another fault a safety goal violation; or does not occur in a safety-related hardware element.

The total failure rate  $\lambda$  for the hardware element is the sum of all faults

$$\lambda = \lambda_{SPF} + \lambda_{RF} + \lambda_{MPF} + \lambda_{SF}. \tag{1.3}$$

#### Safety mechanisms and diagnostic coverage

Safety mechanisms are active or passive components in the item which detect and prevent RHFs from violating a safety goal. The diagnostic coverage (DC) quantifies the proportion of the hardware element failure rate of RFs and latent MPFs faults in percentage which are detected or controlled by the safety mechanisms, see equations 1.4 and 1.5, respectively.

$$K_{\rm DC,RF} = \left(1 - \frac{\lambda_{\rm RF}}{\lambda}\right) \cdot 100 \tag{1.4}$$

$$K_{\rm DC,MPF,L} = \left(1 - \frac{\lambda_{\rm MPF,L}}{\lambda}\right) \cdot 100$$

(1.5)

For the purpose of subsequent hardware architectural metrics calculation, the standard proposes two approaches for DC quantification. One approach is to use a conservative DC value proposed by the standard itself with respect to the type of safety mechanism implemented in the design. Thereby, the DC estimates  $K_{\text{DC,RF}}$  and  $K_{\text{DC,MPF,L}}$  are used to calculate the failure rates  $\lambda_{\text{RF}}$  and  $\lambda_{\text{MPF,L}}$  which are required for hardware architectural metrics calculation. However, generally the conservative DC values are considered too pessimistic and may degrade the hardware design, unnecessarily. To avoid this, a second approach is proposed for DC quantification which is based on the failure mode classification of each individual failure mode of the hardware element in order to obtain the failure rates  $\lambda_{\text{RF}}$  and  $\lambda_{\text{MPF,L}}$  for diagnostic coverage calculation.

| ASIL           | Random hardware failure rate target values |

|----------------|--------------------------------------------|

| $\overline{D}$ | $< 10^{-8} h^{-1}$                         |

| $\mathbf{C}$   | $< 10^{-7} h^{-1}$                         |

| B              | $< 10^{-7} h^{-1}$                         |

Table 1.2: Possible target random hardware failure rates [4].

#### Hardware architectural metrics

Hardware architectural metrics quantify the overall effectiveness of the item against random hardware failures. It accounts for the diagnostic coverage of safety mechanisms as well as for the hardware designs inherent reliability. The hardware architectural metrics respective to single and multi-point faults are calculated using the equations

$$H_{\rm SPFM} = 1 - \frac{\sum_{\rm SR, HW} (\lambda_{\rm SPF} + \lambda_{\rm RF})}{\sum_{\rm SR, HW} \lambda} = \frac{\sum_{\rm SR, HW} (\lambda_{\rm MPF} + \lambda_{\rm S})}{\sum_{\rm SR, HW} \lambda}, \quad (1.6)$$

$$H_{\rm LFM} = 1 - \frac{\sum_{\rm SR, HW} (\lambda_{\rm MPF, L})}{\sum_{\rm SR, HW} (\lambda - \lambda_{\rm SPF} - \lambda_{\rm RF})} = \frac{\sum_{\rm SR, HW} (\lambda_{\rm MPF, P} + \lambda_{\rm MPF, D} + \lambda_{\rm S})}{\sum_{\rm SR, HW} (\lambda - \lambda_{\rm SPF} - \lambda_{\rm RF})},$$

(1.7)

where sum of all safety-related random hardware (SR,HW) failure rates are considered. A high hardware architectural metric indicates high effectiveness of the item against random hardware failures.

#### ASIL achievement

The achievement of the required ASIL is assessed for the item based on the

- 1. sum of all safety-related random hardware failure rates  $\sum_{\text{SR,HW}} \lambda$  and

- 2. hardware architectural metrics  $H_{\mathrm{SPFM}}$  and  $H_{\mathrm{LFM}}$ .

Possible target values for the failure rate and hardware architectural metrics are proposed by the standard and listed in tables 1.2 and 1.3, respectively.

### Fault modelling and fault injection

In terms of fault modelling, the standard addresses only independent random hardware failures, see fig. 1.6 [4]. That is common-cause and cascaded failures are excluded from design verification and safety analysis. Moreover, the generic fault models to be covered are determined by

| Hardware architectural metrics | ASIL B      | ASIL C      | ASIL D      |

|--------------------------------|-------------|-------------|-------------|

| Single-point fault metric      | $\geq 90\%$ | $\geq 97\%$ | $\geq 99\%$ |

| Latent-fault metric            | $\geq 60\%$ | $\geq 80\%$ | $\geq 90\%$ |

Table 1.3: Possible target hardware architectural metrics [4].

- device failure modes,

- layout-dependent shorts and opens (also "direct-current (d.c.)" fault model), and

- soft transient errors.

In the standard, the simulation-based verification using the fault injection technique is explicitly required for the design verification (hardware or system) for completeness and compliance with safety requirements.

System-level and hardware-level design verification The simulation-based verification is required in the product development phase (part 4) for system design verification (part 4, 7.4.8) and hardware design verification (part 5, clause 7.4.4). At system level, it is an obligatory (shall ++) requirement to achieve ASIL D or C. The target is to verify the system design for completeness with the technical safety concept and for compliance with technical safety requirements. At the hardware level, it is an optional (should +) requirement to achieve ASIL D or C. The target is to verify the hardware detailed design including safety mechanisms for compliance and completeness with hardware safety requirements.

Non-conservative determination of diagnostic coverage In part 5, the standard proposes the generic fault models to be considered for the non-conservative determination of diagnostic coverage. The proposed fault models are distinguished depending on the type of hardware element type and the target diagnostic coverage which must be achieved. With respect to the target diagnostic coverage, different fault models must be considered.

Complement to fault injection hardware tests Generally, the fault injection technique is proposed as a hardware test to verify the completeness and correct implementation of safety mechanisms with respect to the hardware safety requirements (part 5, clause 10.4.5). However, as fault coverage of hardware-based fault injection is very low, this is only feasible for

a limited number of faults which can be introduced in a hardware test. To address this, the fault injection is alternatively proposed to be applied on a model of the hardware, e.g. gate-level or transistor-level netlist for which the hardware response can be simulated.

## 1.2 Motivation

Simulation-based functional verification of analog/mixed-signal designs is an important task within IC development. However, the state-of-the-art does not elaborately incorporate the safety-related functional verification in the presence of possible random hardware failures in the circuit. This gives rise to utilize the fault modelling and fault injection technique in this context. Moreover, compliance with ISO 26262 explicitly requires the fault injection technique for system and hardware design verification if informal safety analvsis methods (e.g. FMEA, FTA) are not considered sufficient, also see Annex A A.3.8.2 Verification using fault injection simulation [4]. Additionally, the diagnostic coverage of safety mechanisms is an important factor in hardware architectural metrics calculation and consequently determines the compliance with the target ASIL. Therefore, it must be quantified accurately. For a generic set of safety mechanisms, the standard proposes diagnostic coverage values which are conservative estimates. This means for example that a safety mechanism in an actual design may be much more effective, but by using the conservative value it is degraded for no rational reason. In this context, fault simulation can be utilized to provide a rationale for evidently increasing the diagnostic coverage.

# 1.3 Challenges

The implementation of the pre-silicon safety-related functional verification into the IC development process is associated with a number of challenges in terms of feasibility. The main challenges are explained in this section.

Contrary to the digital domain, for analog fault injection there is generally no well-established methodology. This is mainly due to the difficulty regarding the definition of analog fault models/coverage. Consequently, it is difficult to quantify simulation fault coverage in order to express how well the circuit is exercised by simulation of all possible analog faults.

The analog fault injection technique is not a state-of-the-art automated feature of commercially available CAD tools. However, in order to achieve a high verification confidence, extensive fault injection is necessary which is manually not feasible.

Although the transistor-level/gate-level circuit is suited to achieve high verification confidence, its simulation is computationally demanding if the circuit is complex (e.g. at system level). In order to tackle the simulation time, an adequate fault simulation methodology is required.

# 1.4 Scope of this thesis

The scope of this thesis is to investigate the fault injection technique for safety-related functional verification of automotive Smart Power ICs and therein particularly analog/mixed-signal devices. Based on the state of the art in the analog verification methodology and the fault injection technique, concepts and definitions from the ISO 26262 [4] are used to develop a methodology.

The objectives of this thesis are to achieve high confidence of verification and high quality of safety analysis. Therefore, fault injection and simulation at the gate-level and transistor-level is addressed. However, due to long simulation times and unacceptable manual effort, this is particularly challenging for complex circuit designs and top verification. The work presented in this thesis addresses to tackle these challenges.

## 1.5 Outline

The thesis is divided into seven main chapters.

#### Chapter 2: Related work

Based on a literature research, the related work in the fields of computeraided safety analysis and simulation-based fault injection is presented. Subsequently, a summary is provided.

## Chapter 3: Development of a fault simulation environment

A concept and implementation of an automatic fault injection technique in the <sup>®</sup> Virtuoso<sup>®</sup> CAD tool is described. An object-oriented fault model library and a fault injection algorithm is described. The approach is capable of injection of device-dependent, layout-dependent and functional fault models.

#### Chapter 4: Safety-related functional verification

The scope of the safety-related functional verification within the ISO 26262 is described. Several concepts are described in order to facilitate this in a simulation-based approach. A verification plan is derived from the functional verification plan and the FMEDA. The extraction of hardware architectural level fault models from the FMEDA using the functional fault modelling technique is described. This approach is extended from analog electrical to analog heterogeneous systems.

#### Chapter 5: Fault grouping approach for hierarchical fault injection

A fault grouping approach is proposed for hierarchical fault injection in modular and hierarchical designs. The technique exploits functional fault equivalence at component level and reduces the fault list for top verification. The chapter is divided into two parts: component-level fault injection and fault grouping algorithm. The fault grouping algorithm allows to reduce the fault list based on a hierarchical clustering algorithm and quantitative criteria for the adequacy of the set of fault groups.

#### Chapter 6: Evaluation of soft faults by global sensitivity analysis

For the evaluation of the effects of soft (parametric) faults, an approach based on global sensitivity analysis is proposed. Randomized fault injection is exercised at component level to identify statistically significant soft faults based on their contribution to the output response's variability. Eventually, the fault list for soft faults is reduced by eliminating statistically insignificant faults. Based on the global sensitivity analysis approach, a metric for the simulation fault coverage is proposed.

#### Chapter 7: Experimental results

Experimental results are presented for two safety-related automotive circuits. First, a Lithium-ion cell monitoring and balancing module is considered which is part of a high-voltage battery management system. In the simulation test bench, the module including Lithium-ion cells are represented by behavioural models. Using the simulation-based fault injection, failure modes extracted from the corresponding FMEDA are classified in accordance to ISO 26262 with respect to variations in the application parameters.

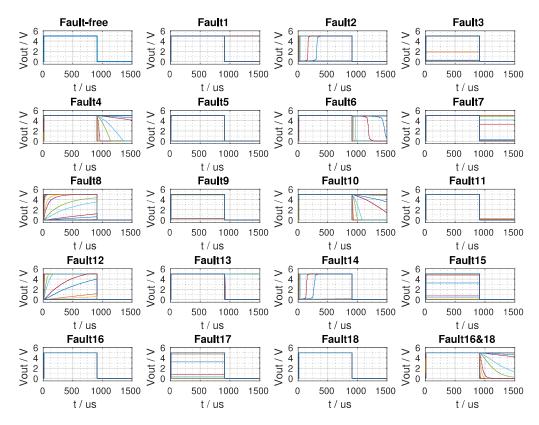

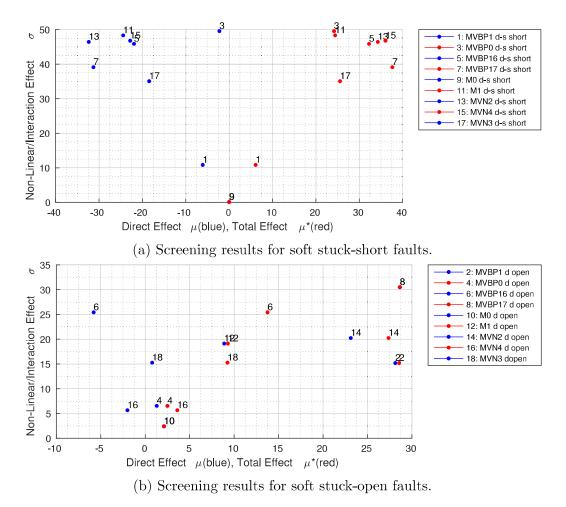

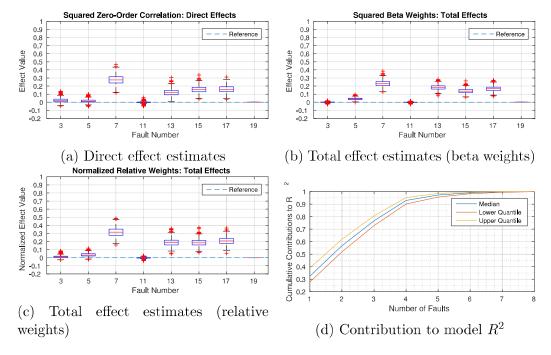

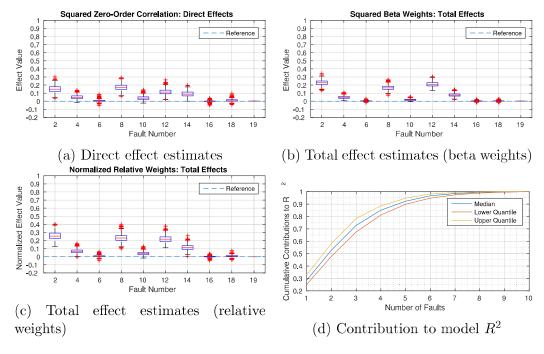

Second, a low-side gate-driver circuit module is considered which is part of a safety-related automotive System-on-a-Chip. In the simulation test bench,