# WIP BALANCE AND DUE DATE CONTROL FOR COMPLEX JOB SHOPS (WAFER FABS)

A Dissertation Presented by Zhugen Zhou

March, 2014

Submitted to die Universit ät der Bundeswehr München in conformity with the requirements for the degree of doctor rerum naturalium (Dr. rer. nat.)

Department of Computer Science Institute of Computer Engineering

1. Supervisor: Prof. Dr. rer. nat. Oliver Rose

2. Supervisor: Prof. Dr. Cathal Heavey

# **ACKNOWLEDGEMENT**

First of all I want to express my gratitude to Prof. Oliver Rose. He gave me the opportunity to do my research in my desired field of interest. He provided excellent research conditions and a high degree of freedom during my research. This dissertation could not have been completed without his guidance and assistance.

I want to thank Sebastian Werner and Frank Lehmann for their great support and fruitful discussion during my stay at Infineon Dresden. Their valuable industrial experiences are big help to this dissertation.

I also want to thank my colleagues in the group of Modeling and Simulation. It is a great pleasure to work with them.

Last I am grateful to my parents and my wife. They gave me support selflessly. I might never have the chance to carry out my study in Germany without their encouragement, patience and tolerance.

#### **Abstract:**

Nowadays to survive in the global market with increasing and fierce competition, the keys to success for the companies are fast product and reliable delivery that are the challenges for shop floor control. As one of the most important key performance indicators (KPI), work-in-process (WIP) attracts more and more attention since it has a major influence on overall manufacturing costs. According to Little's Law, a lower WIP level leads to a shorter production cycle time given the same throughput, which has significant economic importance. Besides that, due date commitment is another critical factor, especially for customer oriented companies to achieve customer satisfaction. A missed due date causes not only penalty, but also confidence lost to the customers.

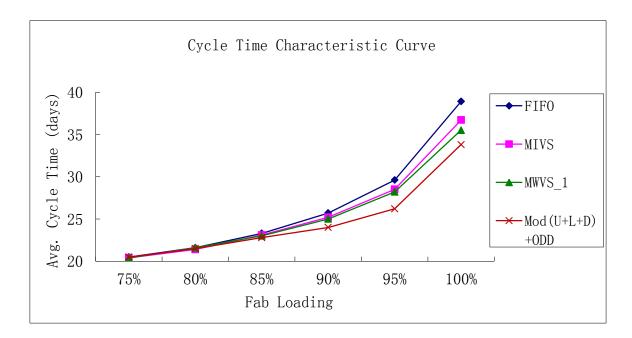

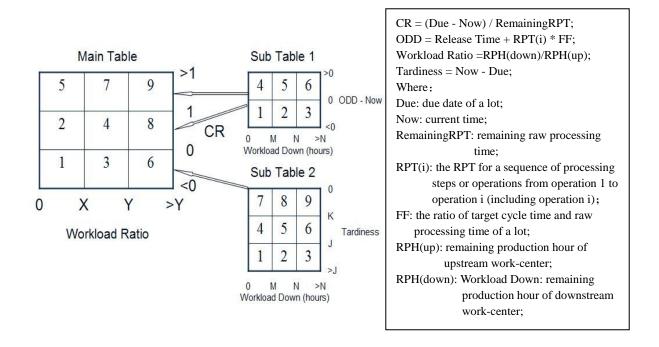

In order to gain a competitive position within industry, on the shop floor enormous efforts have been spent in developing different kinds of operational control strategies relating to WIP and due date. On one hand, there are a number of operational control strategies which target the control of the flow of lots through wafer fab to achieve balanced WIP like CONstant WIP (CONWIP), Starvation Avoidance (SA), or Minimum Inventory Variability Scheduling (MIVS). These WIP oriented rules attempt to avoid starvation and congestion of work-center or operation, thus reducing WIP variability and cycle time. On the other hand, there are also a number of dispatching rules targeting due date control like Earliest Due Date (EDD), Critical Ratio (CR) and Operation Due Date (ODD). These due date oriented rules focus on progressing lot toward on-time completion based on lot status. As WIP and due date have two different goals, even conflicting goals under certain circumstances, the first set of WIP oriented rules do not always lead to good on-time delivery performance, the

latter due date oriented rules do not primarily lead to low WIP level. Both WIP oriented and due date oriented rules turn out to be insufficient when both targets, i.e., lower WIP level and lower cycle time, better on-time delivery and less tardiness, are desired simultaneously.

As a matter of fact, on the shop floor the challenges to apply WIP oriented or due date oriented rules are way beyond our anticipation. We encounter plenty of questions that cannot be answered with satisfaction from existing literature, when we manage to apply WIP oriented or due date oriented rules. The motivation of this dissertation is to find out the answers for the concerned issues relating to WIP and due date from industry. Particularly, we have a stronger interest in WIP related issues and intend to carry out a comprehensive study about WIP, for the reason that for instance low WIP level in combination with low variance can make sure the lots finish before their due dates as much as possible. Naturally, the due date related issues (on-time delivery and tardiness) can be solved perfectly. We will address the following eight issues and attempt to find out the answers in this dissertation.

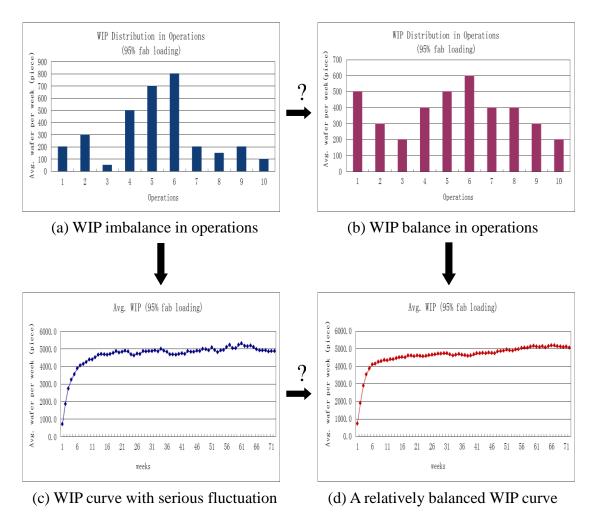

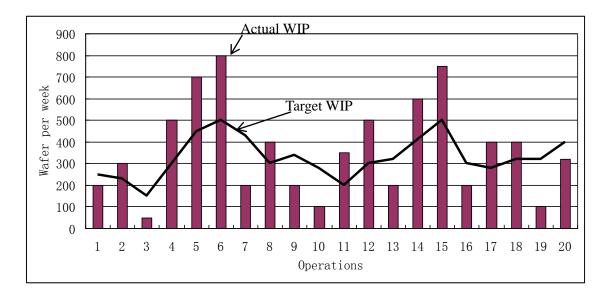

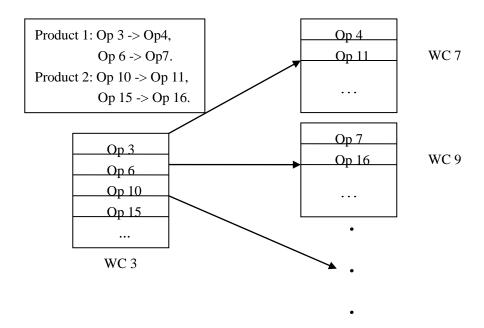

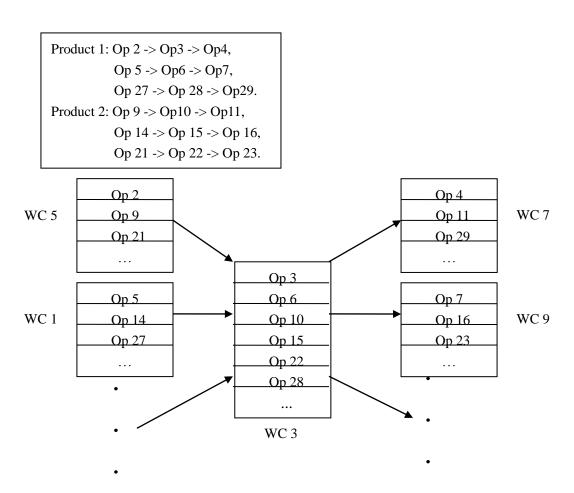

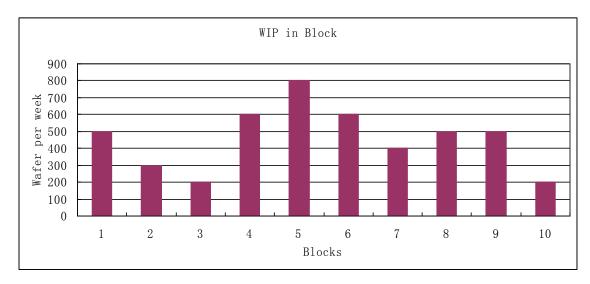

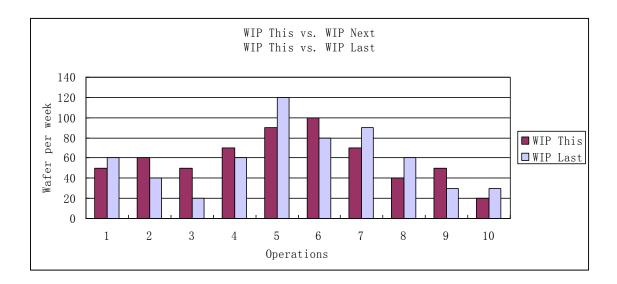

The first one is **work-center oriented WIP balance**. The classic WIP balance rules like MIVS and Line Balance algorithm (LB) are operation oriented. Some researchers claim that managing WIP from the viewpoint of operations is beneficial because the WIP flow histogram intuitively tells us that we should push WIP from high WIP operation to low WIP operation. Nevertheless, the disadvantage of operation orientation that is to disregard the workload status of work-center is also obvious. In particular, it tends to cause congestion when work-centers have breakdowns. Therefore, some engineers would prefer to look at WIP flow at the viewpoint of work-center, which brings forward the first issue that is work-center oriented WIP balance.

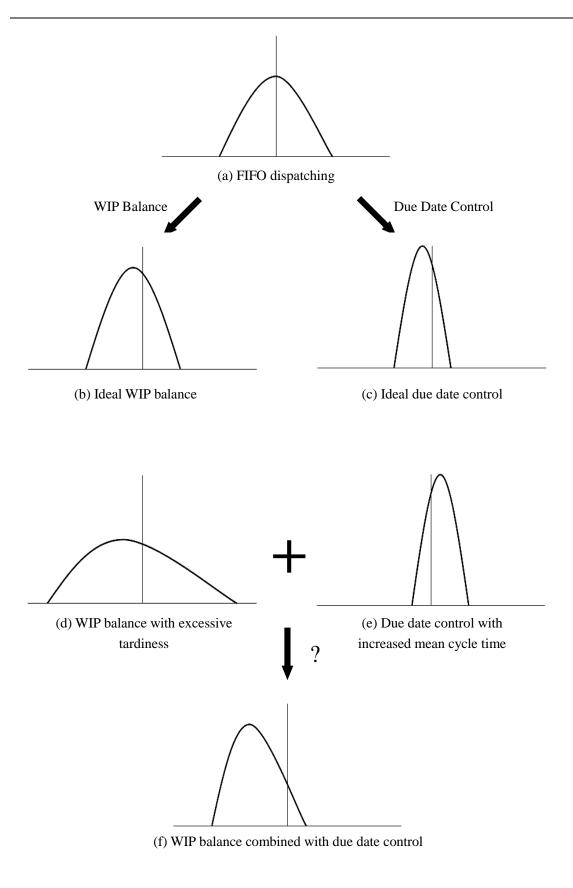

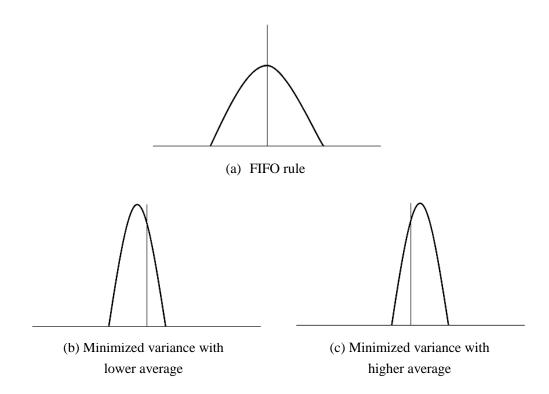

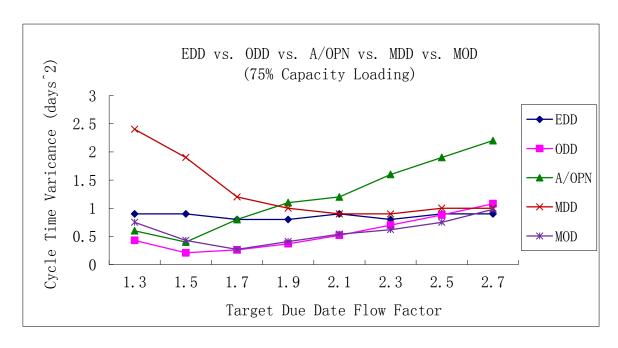

The second issue, **fast but poor pace lot movement**, arises from the first issue. It is no doubt that work-center oriented WIP balance can achieve low WIP levels and low average cycle times for the fab. Whereas, without consideration of the lot status, i.e., whether a lot is ahead of/on/behind schedule (also expressed as due date information), some lots are accelerated while some are waiting long time in the queue. This poor pace movement causes a high cycle time variance which becomes a potential problem if good on-time delivery is desired. How to improve the lot movement based on WIP balance is particularly important to due date control.

No matter whether applying operation oriented or work-center oriented WIP balance, both can lead to two research directions which are to apply them with or without target WIP levels. The third issue is about how to determine the target WIP level for work-centers. The reason why the classic rule MIVS is successful is due to the assistance of target WIP. The target WIP regulates the WIP flow to avoid starvation and congestion. How to set an adequate WIP level is a challenging task because the performance of such a WIP balance approach is sensitive and highly relies on the target WIP level. The target WIP level usually has to be set appropriately by means of pilot studies or educated guessing. Therefore, an adaptive procedure or sophisticated approach to determine the adequate WIP level should be considered like applying queuing model or neural network based on the historical data.

The fourth issue that is **work-center oriented balance without the need of target WIP** is an extension of the third issue. From operational control viewpoint, there are many reasons to abandon the application of target WIP despite the fact that target WIP is helpful and effective. For instance, uncertainty of product volume mix and almost daily changing lot release rates due to

frequent changes of customer orders cause the necessity to update the target WIP daily, or even hourly. Not to mention that huge parameter sets for the simulation experiment imposes additional challenges to apply target WIP.

The fifth issue is an extension to the first and second issues. The reason why WIP oriented and due date oriented rules harm each other in some cases is because they only employ their favorable information. It tells us that if we expect to make an optimal dispatching decision, we need to take the workload information of work-centers as well as the lot status information (due date information) into consideration. As a result, a new dispatching scenario including WIP information and due date information is desired.

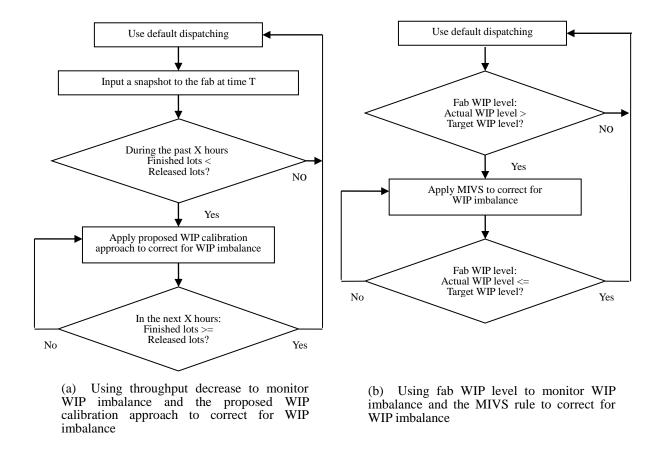

No matter how much effort we spend to achieve WIP balance, WIP imbalance can still occur anytime and anywhere in the fab, since it is time dependent. The sixth issue is about WIP imbalance monitoring and calibration. Even small WIP imbalances can grow to serious problems if they could not be restrained in time. Therefore, an effective mechanism to monitor and detect WIP imbalances is necessary. In the literature, researchers have proposed WIP monitoring and calibration approaches which utilize the target WIP as trigger event and the MIVS rule as a calibration method. Once again, we propose a new WIP imbalance detection and calibration approach to differentiate from the one using target WIP. The reason is obvious and analogous to the fourth issue.

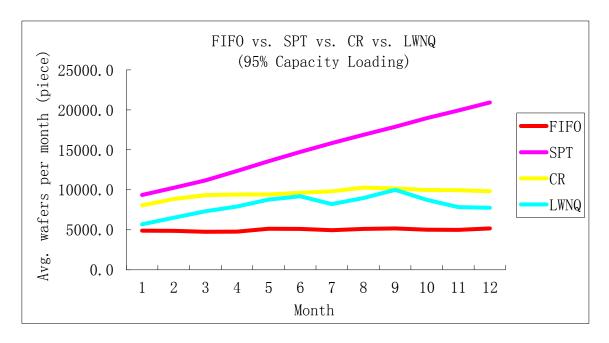

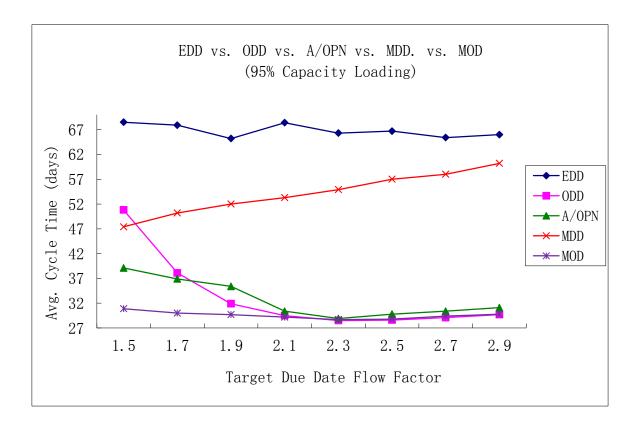

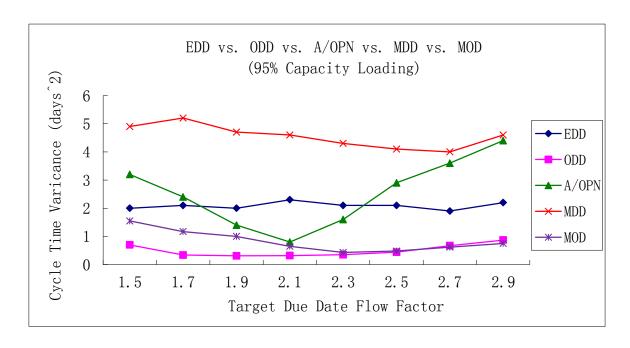

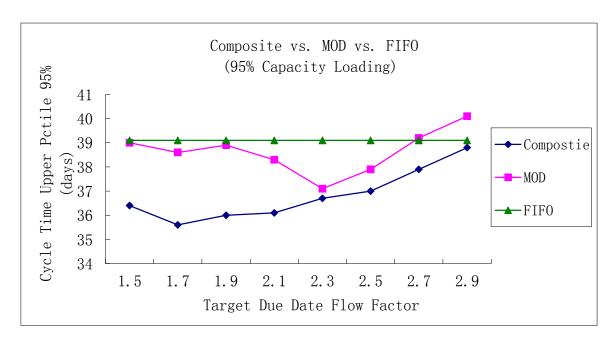

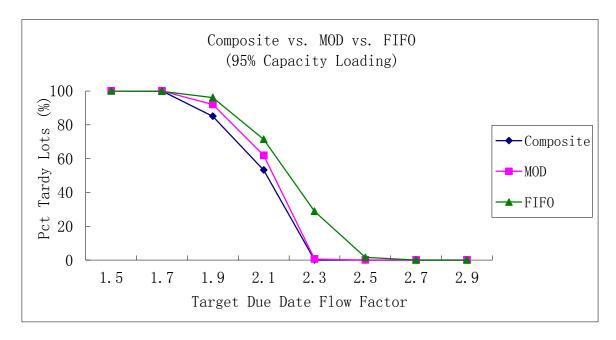

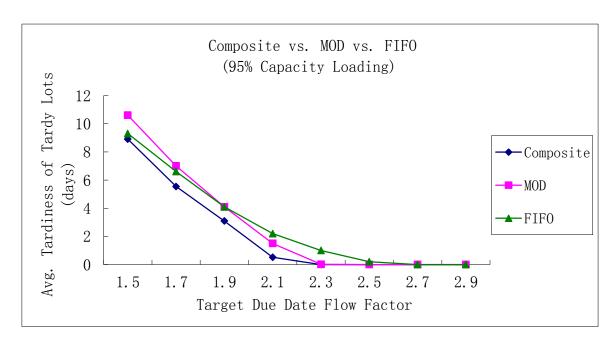

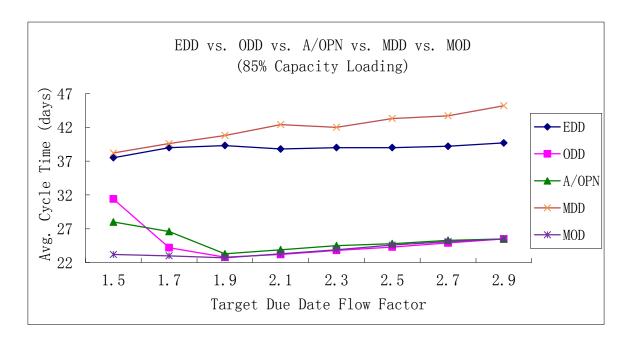

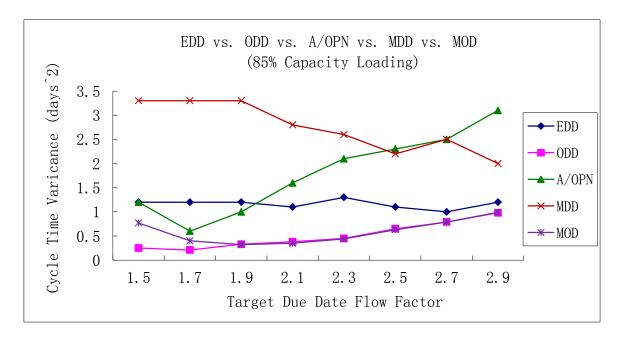

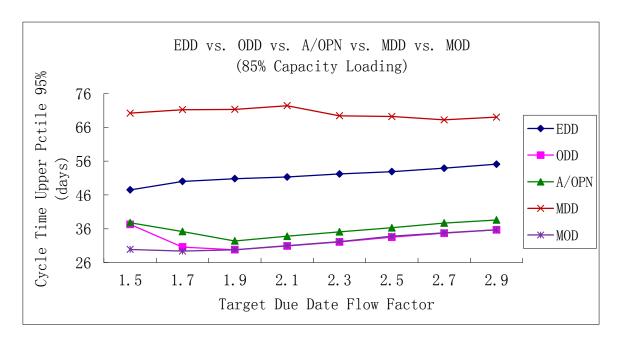

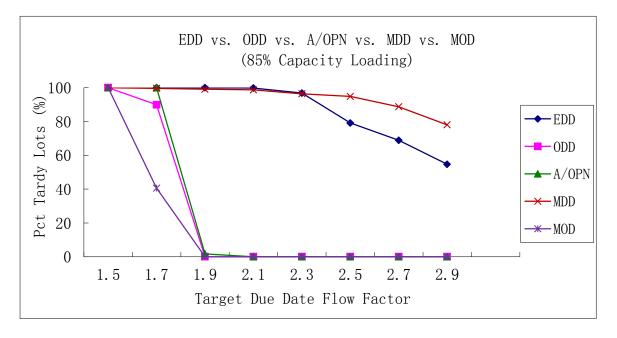

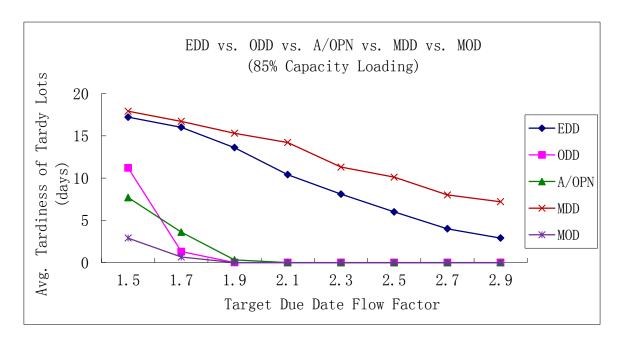

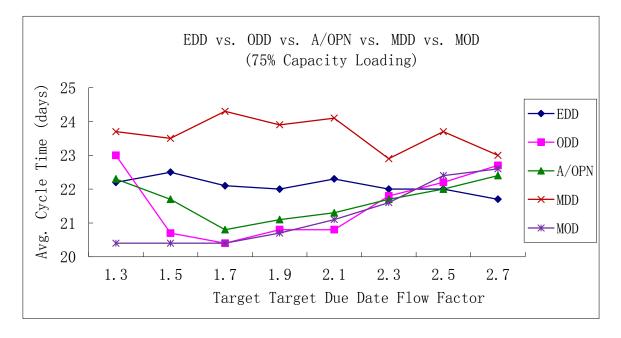

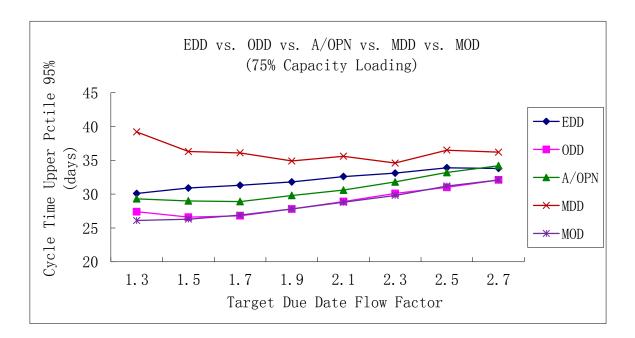

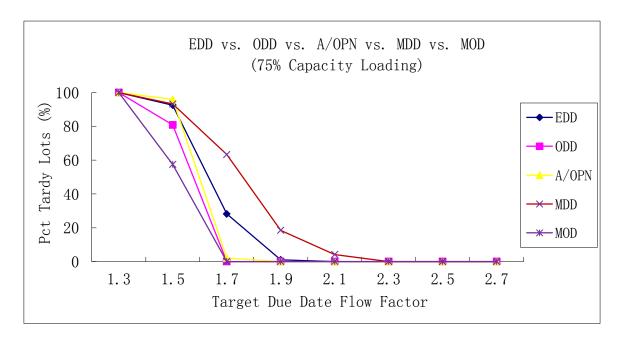

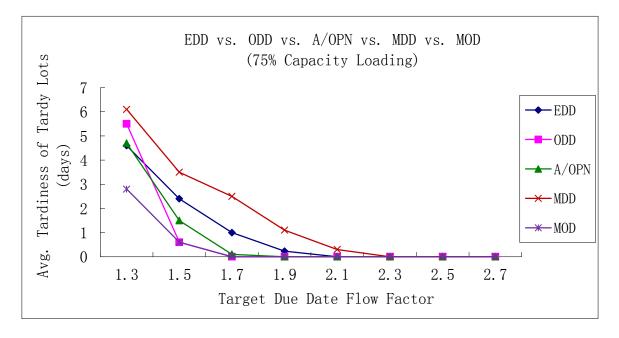

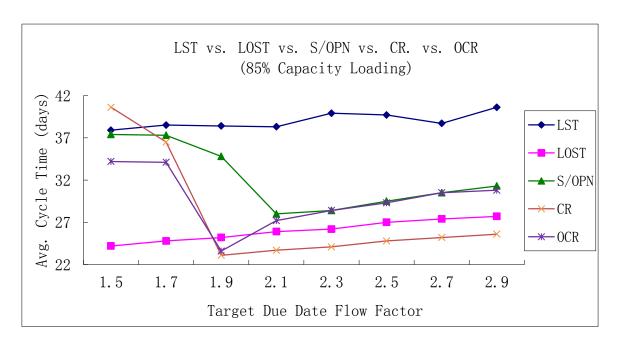

The seventh issue is **the performances of due date oriented rules** in literature. This issue looks independently from the above issues at first glance, actually, they connect to each other. On one hand, we spend much effort to figure out the cause of WIP imbalance, and we realize that the due date rules have a common symptom that WIP imbalance occurs under tight due dates and

high capacity loading. It demonstrates that we should pay more attention when the fab runs products with tight due dates and under high fab loading. On the other hand, the inherent characteristic of due date rules is to reduce lateness variance, thus reducing cycle time variance, which can exactly overcome the drawback arising from WIP balance for work-centers. Furthermore, the variants of due date rules - composite rules, e.g., modified operation due date (MOD), solve the WIP imbalance problem under tight due dates successfully, which gives us a hint to deal with the confliction between WIP balance and due date control.

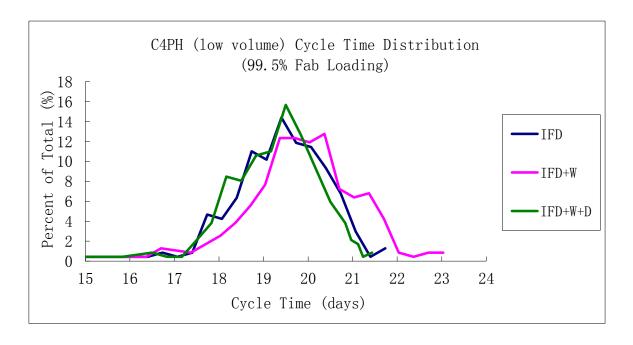

When we obtain an insight into WIP balance and due date control, the eight issue is about how to combine both ideas, i.e., keeping a low WIP level, avoiding bottleneck starvation and meeting due dates. In reality, the fact is sometimes that we cannot achieve both targets, and the question which one is more important is controversial and has been raised by academic and industrial researchers. The answer is that it depends on the objective and situation in the fab. For example, in a customer oriented wafer fab there are some low volume products like hot lots, engineering lots and customer sample are expected to leave the fab as fast as possible. Normally, they will be assigned tight due dates to be accelerated. However, the introduction of WIP balance to this kind of wafer fabs seems to reduce the weight of due date control to low volume products. In order to make better trade-off between WIP balance and due date control, we have to figure out the interaction between them first. We intend to carry out preliminary study about this issue in this dissertation.

**Key words**: Wafer fabs, dispatching rule, WIP balance, cycle time reduction, due date control, on-time delivery

# Chapter

| 1.    | Introduction                                                                                             | 1          |

|-------|----------------------------------------------------------------------------------------------------------|------------|

| 1.1   | Challenges and Motivation                                                                                | .1         |

| 1.2   | Problem Definition                                                                                       | .4         |

| 1.3   | Objectives                                                                                               | .8         |

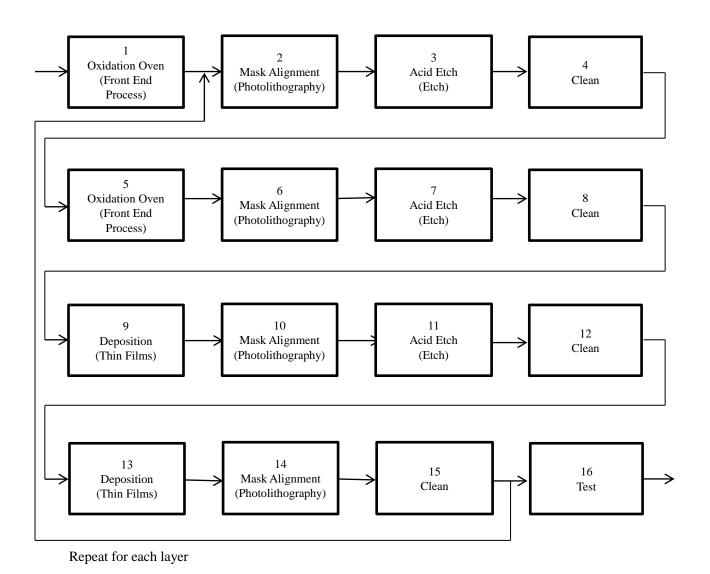

| 1.4   | Wafer Fabrication Facilities (Wafer Fabs)                                                                |            |

| 1.5   | Structure of this Dissertation                                                                           |            |

| _     |                                                                                                          |            |

| 2.    | Methodologies for Wafer Fabs2                                                                            | U          |

| 2.1   | Important Performance Indicators in Wafer Fabs2                                                          | 0          |

| 2.2   | Literature Review2                                                                                       | 25         |

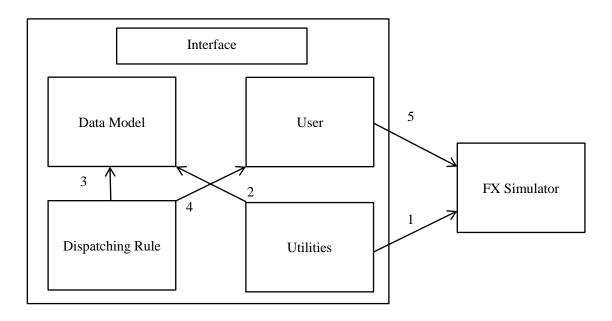

| 2.3   | Simulation Model and Software                                                                            | 37         |

| 3.    | Work-center Oriented WIP Balance4                                                                        | 3          |

| 3.1   | Work-center Oriented WIP Balance                                                                         | 14         |

| 3.1.1 | WIP Imbalance Symptoms in Wafer Fabs (MIMAC6 Model)                                                      | 44         |

| 3.1.2 | Minimum Inventory Variability Scheduling (MIVS) - Operation Oriented W                                   | IP         |

|       | Balance                                                                                                  | 48         |

| 3.1.3 | Minimum Workload Variability Scheduling (MWVS) - Work-center Oriented W                                  | IP         |

|       | Balance                                                                                                  | 51         |

| 3.1.4 | Conclusions                                                                                              | 54         |

| 3.2   | Cycle Time Variance Reduction                                                                            | <b>5</b> 7 |

| 3.2.1 | Why Cycle Time Variance Reduction is Necessary                                                           | 67         |

| 3.2.2 | Rules to Minimize Cycle Time Variance                                                                    | 68         |

| 3.2.3 | Simulation Results and Performance Analysis                                                              | 75         |

| 3.2.4 | Conclusions                                                                                              | 79         |

| 3.3   | Using Queuing Models and Neural Networks to Determine Targ WIP Levels for Work-centers for MWVS Approach |            |

|                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.1                                        |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| 3.3.1                                                                                            | Introduction to Queuing Models and Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81                                         |  |  |

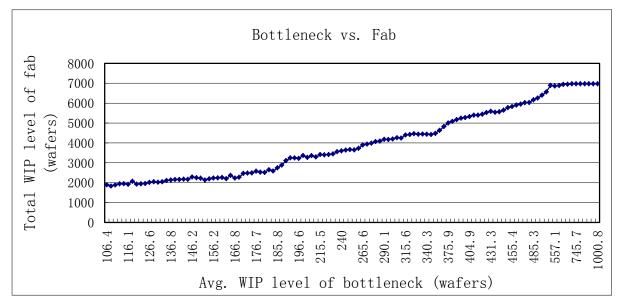

| 3.3.2                                                                                            | Estimating Target WIP Levels for Bottleneck Work-centers Using Queuing Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |  |  |

|                                                                                                  | under 75%, 85% and 95% Fab Capacity Loadings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84                                         |  |  |

| 3.3.3                                                                                            | Estimating Target WIP Levels for Wafer Fabs under 75%, 85%, 95% Fab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Loadings                                   |  |  |

|                                                                                                  | Using Feed-forward Back-propagation Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85                                         |  |  |

| 3.3.4                                                                                            | Allocating Average WIP Level to Each Non-bottleneck Work-center from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | the Total                                  |  |  |

|                                                                                                  | WIP Level of the Fab under 75%, 85% and 95% Fab Loadings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91                                         |  |  |

| 3.3.5                                                                                            | Simulation Results and Performance Analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92                                         |  |  |

| 3.3.6                                                                                            | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96                                         |  |  |

| 3.4                                                                                              | <b>Due Date Control - Due Date Oriented Rules</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 99                                         |  |  |

| 3.4.1                                                                                            | The Characteristics of Due Date Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99                                         |  |  |

| 3.4.2                                                                                            | Due Date Oriented Rules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101                                        |  |  |

| 3.4.3                                                                                            | Due Date Tightness Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 400                                        |  |  |

| 5.4.5                                                                                            | Due Date Tightness Setting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108                                        |  |  |

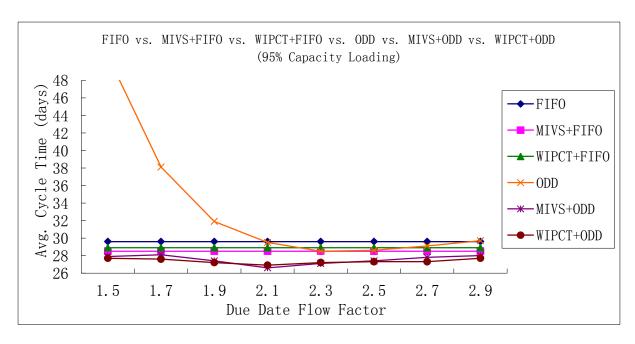

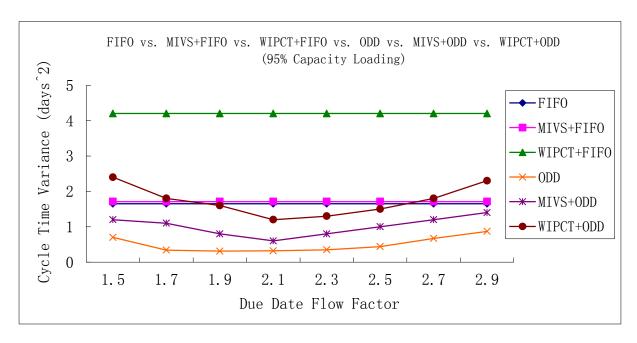

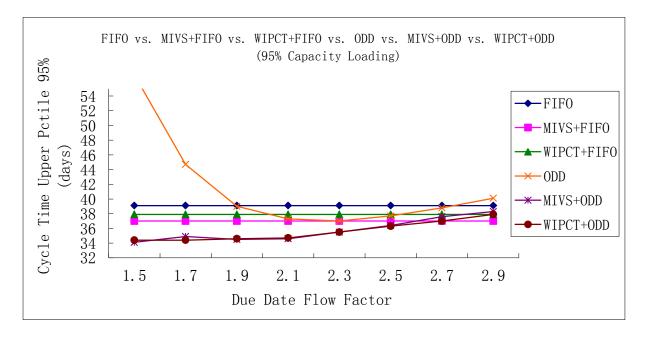

|                                                                                                  | Simulation Results and Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |  |  |

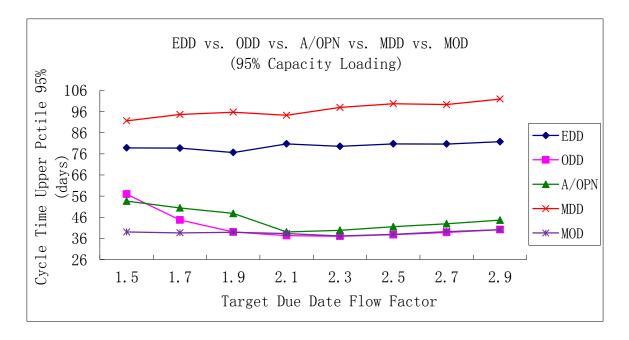

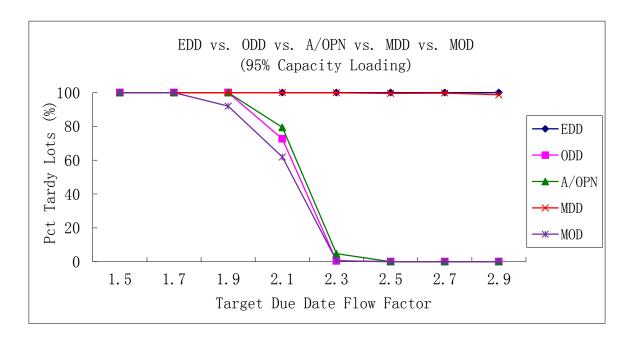

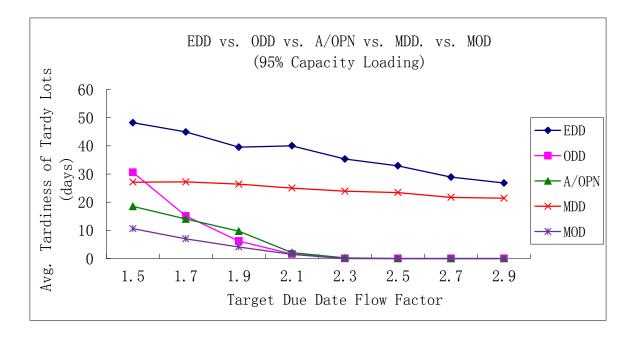

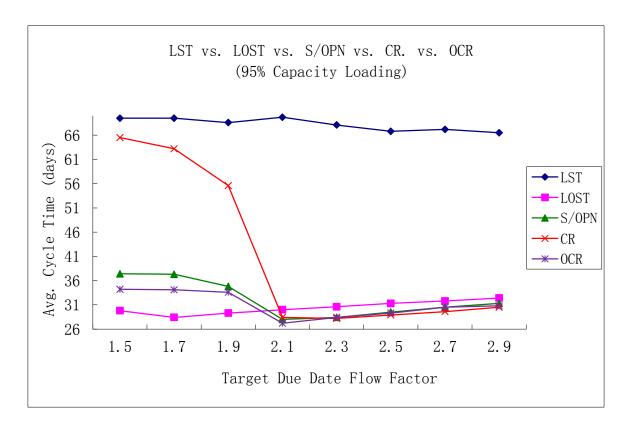

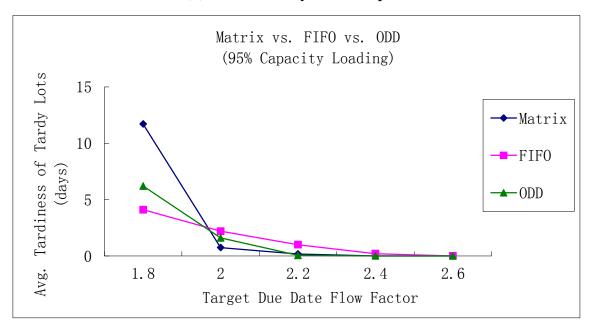

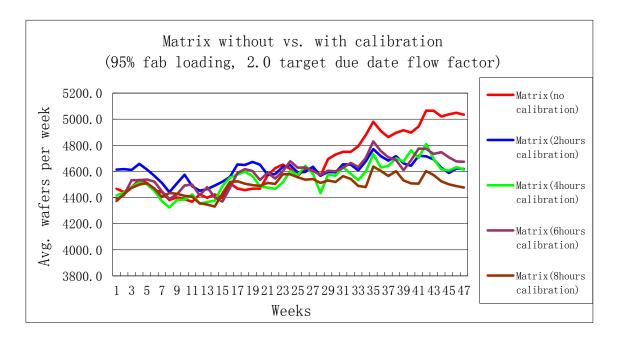

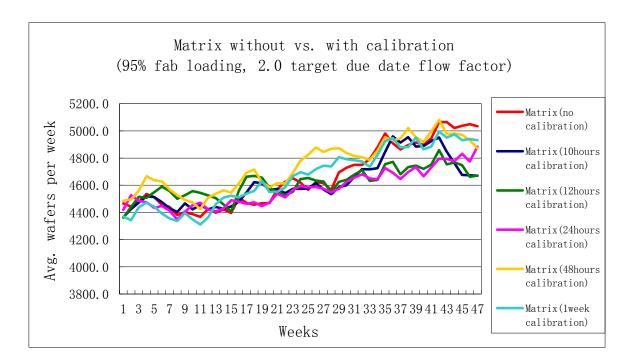

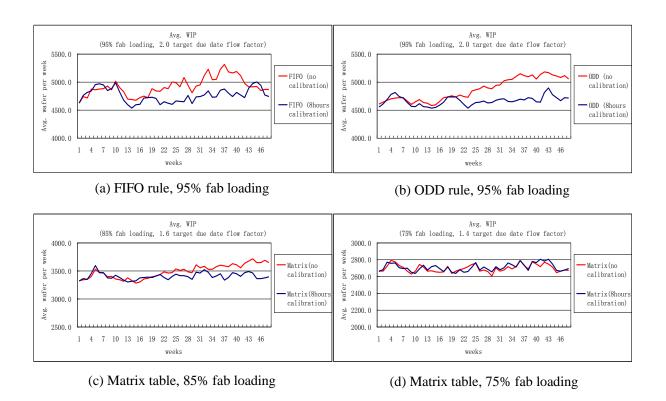

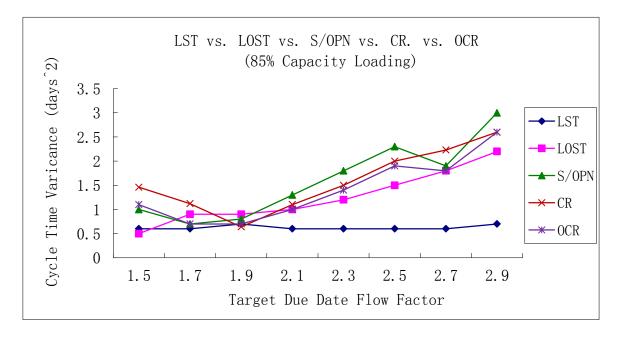

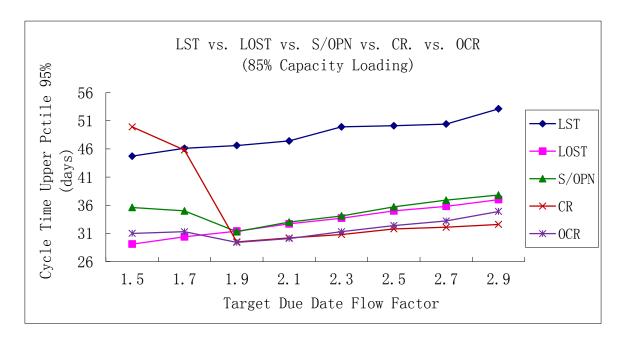

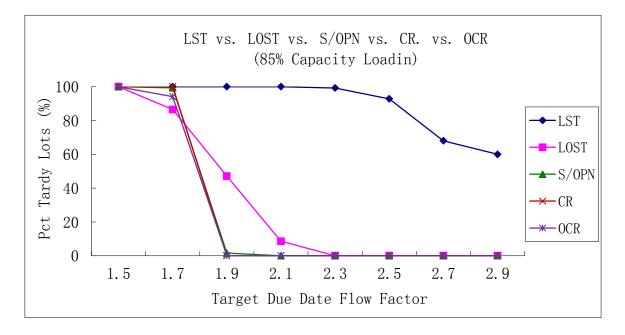

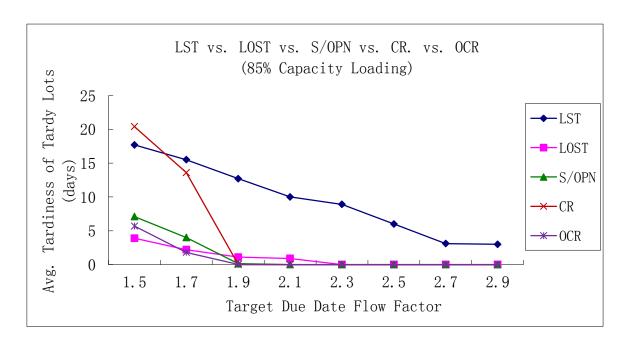

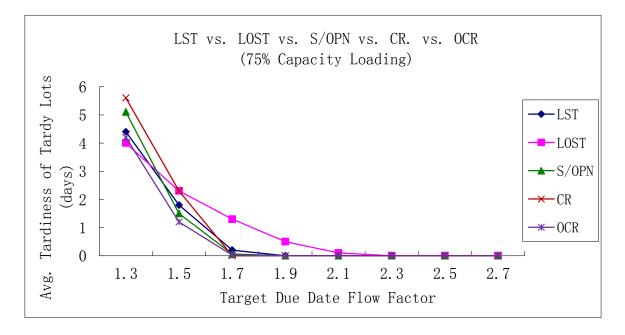

| 3.4.4<br>3.4.5                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110<br>119                                 |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b>                                                                      | Simulation Results and Performance Analysis.  Conclusions  Extension to Work-center oriented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110<br>119<br>122                          |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b>                                                                      | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110119122 -center                          |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b>                                                                      | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110119122 -center                          |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b>                                                                      | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of Scheme | 110 WIP122 -center Farget                  |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b><br>4.1                                                               | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 110 WIP122 -center Farget123               |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b>                                                                      | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 110119122 -center Farget123123             |  |  |

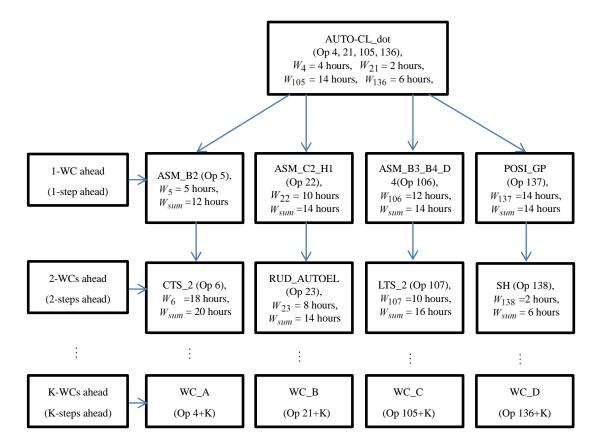

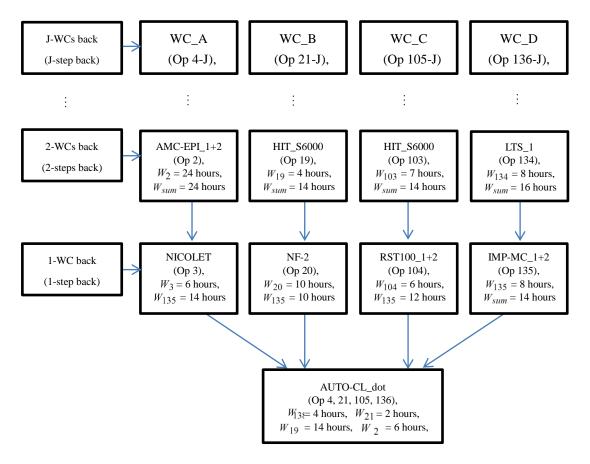

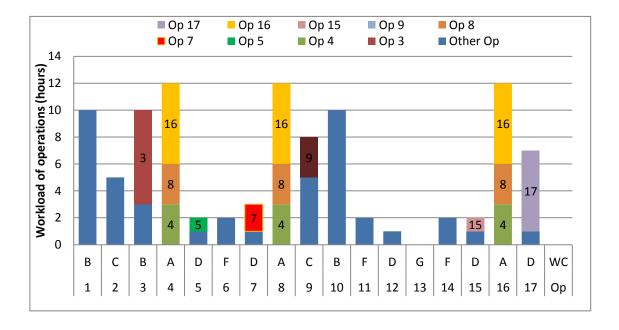

| 3.4.4<br>3.4.5<br><b>4.1</b><br>4.1.1<br>4.1.2                                                   | Simulation Results and Performance Analysis  Conclusions  Extension to Work-center oriented Balance  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110119122 -center Farget123123             |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b><br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                  | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.  Simulation Results and Performance Analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110119122 -center Farget123123126140       |  |  |

| 3.4.4<br>3.4.5<br><b>4.</b><br><b>4.1</b><br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br><b>4.2</b>      | Simulation Results and Performance Analysis  Conclusions  Extension to Work-center oriented Balance  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.  Simulation Results and Performance Analysis.  Conclusions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110119122 -center Farget123123140145       |  |  |

| 3.4.4<br>3.4.5<br><b>4.1</b><br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br><b>4.2</b><br>4.2.1          | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.  Simulation Results and Performance Analysis.  Conclusions.  WIP Control and Calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110119122 -center Farget123123140145148    |  |  |

| 3.4.4<br>3.4.5<br><b>4.1</b><br>4.1.1<br>4.1.2<br>4.1.3                                          | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.  Simulation Results and Performance Analysis.  Conclusions.  WIP Control and Calibration.  The Necessity of WIP Control and Calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110119122 -center Farget123130140145148148 |  |  |

| 3.4.4<br>3.4.5<br><b>4.1</b><br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br><b>4.2</b><br>4.2.1<br>4.2.2 | Simulation Results and Performance Analysis.  Conclusions.  Extension to Work-center oriented Balance.  A Global WIP Oriented Dispatching Scheme: Work Workload Balance without Requirement of WIP.  Why Abandon Target WIP.  Workload Indicator (WI) to Measure the Pull Request of Work-center.  Simulation Results and Performance Analysis.  Conclusions.  WIP Control and Calibration.  The Necessity of WIP Control and Calibration.  Priority Matrix Table for WIP Control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 110119122 -center Farget123140145148148151 |  |  |

| 5.    | WIP Balance Combining with Duc Control                                                              |                 |

|-------|-----------------------------------------------------------------------------------------------------|-----------------|

| 5.1   | Incorporating Due Date Oriented Rules into WII Approach to Achieve Cycle Time Reduction and On-time |                 |

|       | Improvement                                                                                         | 176             |

| 5.1.1 | What Happens When WIP Balance Meets Due Date                                                        | 176             |

| 5.1.2 | Introduction to WIPCT                                                                               | 180             |

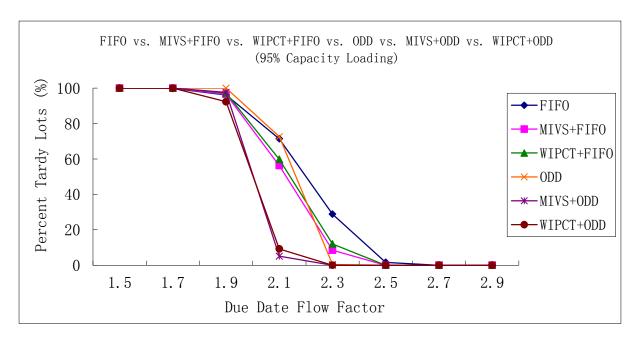

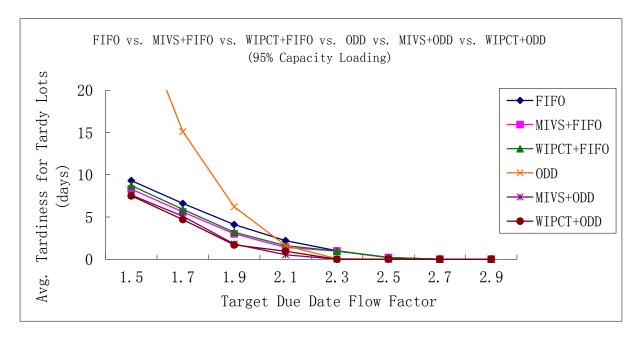

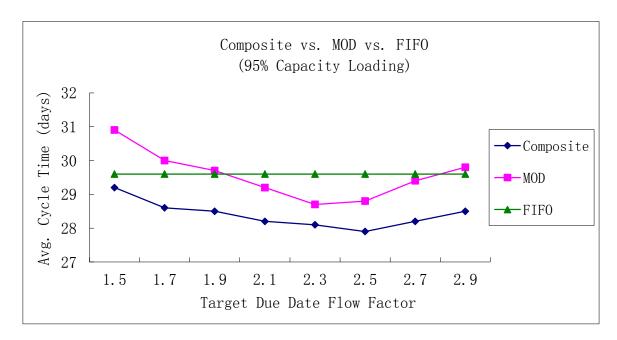

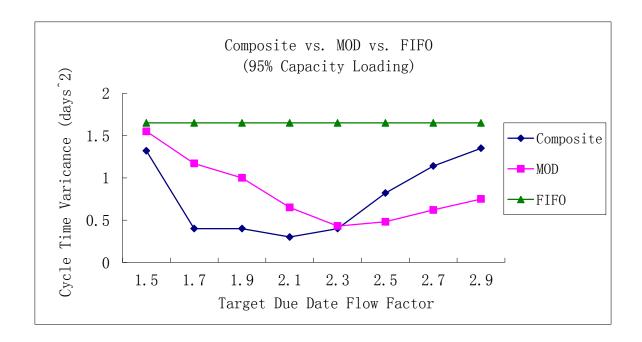

| 5.1.3 | Simulation Results and Performance Analysis                                                         | 182             |

| 5.1.4 | Conclusions                                                                                         | 189             |

| 5.2   | A Composite Rule Combining WIP Balance and                                                          | <b>Due Date</b> |

|       | Control                                                                                             | 191             |