### UNIVERSITÄT DER BUNDESWEHR MÜNCHEN Fakultät für Elektrotechnik und Informationstechnik (Institut für Physik)

## Molecular Beam Deposition (MBD) and Characterisation of High-k Material as Alternative Gate Oxides for MOS-Technology

Dissertation von

Vanessa Capodieci

Februar 2005

## **Abstract**

Until now the forecast of the Semiconductors Industry Association (SIA) concerning the dimension shrinking and the performance improvement of the electrical devices, reported in the International Technology Roadmap for Semiconductors (ITRS), matched very precisely the development of semiconductor process technology. But today the traditional scaling is indeed approaching the fundamentals limits of the materials constituting the building blocks of the CMOS process. A big and unresolved challenges in the traditional process shrinking approach is the gate insulator. To be able to follow the dimension shrinking according to the ITRS, the SiO<sub>2</sub> film thickness should become below 1nm within the next three years. This thickness corresponds to few atomic layers, which means that the direct tunnel leakage current through the insulator will increase. The high leakage current and the inadequate reliability for a SiO<sub>2</sub> layer of less than 1.5nm thickness require a replacement for SiO<sub>2</sub>. To obtain high gate capacitance and inhibit tunneling, relative thick insulator of high dielectric constant (high-k) are needed to replace silicon dioxide (SiO<sub>2</sub>) as gate oxide. Therefore new materials have to be introduced into the basic CMOS structure to replace the existing ones to further extend device scaling and the reduction of the production costs.

The present research thesis focuses on the proposition and investigation of three alternative gate oxide systems: aluminium-, praseodymium and lanthanum oxide (Al<sub>2</sub>O<sub>3</sub>, Pr<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub>, respectively). For each one of these system, the growth process by Molecular Beam Deposition (MBD) has been optimised and electrical and physical characterisation has been performed to gain a better understanding of important factors associated with alternative gate dielectrics from both a theoretical and experimental points of view. Moreover, the optimisation of the interface between gate dielectric and the silicon substrate is taken into account during the development of the deposition processes.

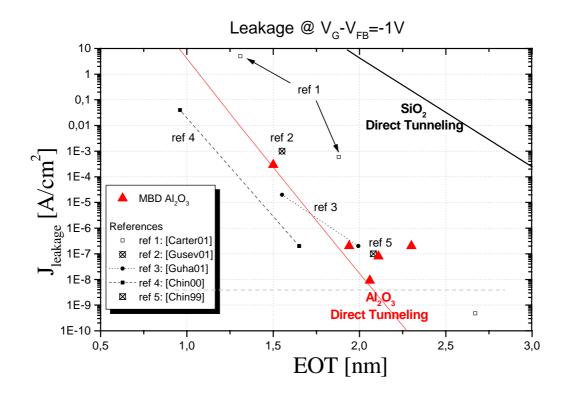

The first part of the thesis concerns the aluminium oxide. Aluminium oxide  $(Al_2O_3)$  is one of the first systems which have been studied to replace silicon dioxide as gate dielectric because of its large barrier height, dielectric constant twice that of  $SiO_2$ , high stability and robustness. The basic properties of  $Al_2O_3$  films grown on silicon substrate are well understood and for this reason alumina can be used as reference to investigate on new materials for alternative gate oxide .

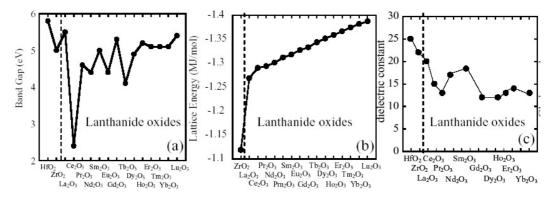

Beyond the aluminium oxide, lanthanide oxides have been considered as long term solution to the high-k question. In particular praseodymium oxide  $(Pr_2O_3)$  and lanthanum oxide  $(La_2O_3)$  have attracted the attention because of their high dielectric constant (20-30) and thermal stability on silicon substrate until 1000K.

The properties of thin lanthanide oxide films as dielectric system for microelectronic application are not yet completely known and intensive research is running to find out if this dielectric will cover all the requirement needed for the new gate oxide material. In particular the major drawback of lanthanide oxide is given by its high sensibility to humidity, which leads to degradation of the dielectric film.

This thesis will try to give an answer to the open questions on the investigated materials and will show the direction for future investigations.

# **Contents**

|   | Abst  | ract         |                                                                                         |        |

|---|-------|--------------|-----------------------------------------------------------------------------------------|--------|

| 1 | Intro | duction      |                                                                                         | 1      |

|   | 1.1   | Dimension    | n Shrinking in CMOS Technology                                                          | 1      |

|   | 1.2   | Alternativ   | re gate dielectrics                                                                     | 2      |

|   | 1.3   | Scope of t   | the present research and thesis outline                                                 | 6      |

| 2 | Depo  | sition and ( | Characterisation Methodologies                                                          | 8      |

|   | 2.1   | Molecular    | Beam Deposition                                                                         | 9      |

|   |       | 2.1.1 M      | BD of Alternative Gate Dielectrics                                                      | 11     |

|   | 2.2   | Electrical   | Characterisation Methods                                                                | 13     |

|   |       | 2.2.1 C(     | V) measurements                                                                         | 13     |

|   |       | 2.2.1.1      | C(V) and G(V) data acquisition and analysis                                             | 14     |

|   |       | 2.2.2 Int    | terface State Characterisation                                                          | 16     |

|   |       | 2.2.3 I(V    | V) measurements                                                                         | 18     |

|   | 2.3   | Physical a   | and Chemical Characterisation Methods                                                   | 19     |

|   |       | 2.3.1 X-     | ray Photoelectron Spectroscopy – XPS                                                    | 19     |

|   |       | 2.3.2 Au     | ager Electron Spectroscopy – AES                                                        | 20     |

|   |       | 2.3.3 Ru     | therford BackScattering Spectroscopy – RBS                                              | 21     |

|   |       | 2.3.4 Tr     | ansmission Electron Microscopy – TEM                                                    | 23     |

| 3 | Depo  | sition Proc  | ess optimisation and characterisation of thin Al <sub>2</sub> O <sub>3</sub> films      | 25     |

|   | grow  | n by means   | s of MBD                                                                                |        |

|   | 3.1   | Physical p   | properties of Al <sub>2</sub> O <sub>3</sub>                                            | 25     |

|   | 3.2   | Process of   | ptimisation and thermal stability of MBD-grown Al <sub>2</sub> O <sub>3</sub> thin film | s . 27 |

|   |       | -            | fluence of substrate temperature                                                        |        |

|   |       |              | fluence of oxygen partial pressure                                                      |        |

|   |       |              | zone enhanced growth of aluminium oxide                                                 |        |

|   |       |              | fluence of the annealing ambient                                                        |        |

|   |       |              | fluence of the Si-substrate preparation before $Al_2O_3$ deposition.                    |        |

|   | 3.3   |              | Characterisation                                                                        |        |

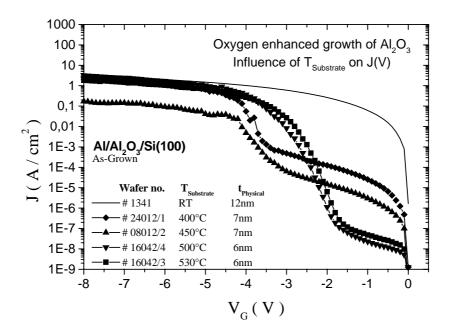

|   |       |              | arrent density vs. voltage (J-V) measurements                                           |        |

|   |       | 3.3.1.1      |                                                                                         |        |

|   |       | 3.3.1.2      | • , ,                                                                                   |        |

|   |       | 3.3.1.3      |                                                                                         |        |

|   |       | 3.3.1.4      |                                                                                         |        |

|   |       |              | anacitance vs. voltage (C-V) measurements                                               | 37     |

|   |                     | 3.3                                                                                          | .2.1 Ozone enhanced growth of aluminium oxide                                                                                                                             | 37                              |

|---|---------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   |                     | 3.3                                                                                          | .2.2 Optimisation of the annealing process                                                                                                                                | 40                              |

|   |                     | 3.3                                                                                          | .2.3 $C(V)$ characterisation of MBD-grown $Al_2O_3 \ldots \ldots$                                                                                                         | 42                              |

|   |                     | 3.3.3                                                                                        | Comparison of MBD-Al <sub>2</sub> O <sub>3</sub> with SiO <sub>2</sub> and Literature                                                                                     | 44                              |

|   |                     | 3.3.4                                                                                        | Parameters for an optimised MBD process of Al <sub>2</sub> O <sub>3</sub>                                                                                                 | 45                              |

|   | 3.4                 | Physic                                                                                       | cal Analysis of MBD-grown Al <sub>2</sub> O <sub>3</sub> thin films                                                                                                       | 46                              |

|   |                     | 3.4.1                                                                                        | SIMS                                                                                                                                                                      |                                 |

|   |                     | 3.4.2                                                                                        | AES                                                                                                                                                                       | 47                              |

|   |                     | 3.4.3                                                                                        | XPS                                                                                                                                                                       |                                 |

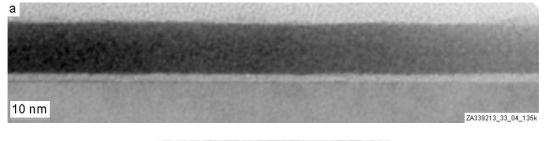

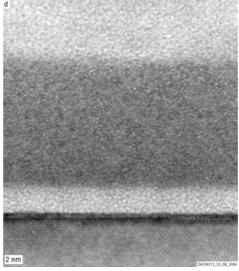

|   |                     | 3.4.4                                                                                        | TEM                                                                                                                                                                       |                                 |

|   | 3.5                 | Conclu                                                                                       | usion                                                                                                                                                                     | 50                              |

| 4 | Inter               | face En                                                                                      | gineering                                                                                                                                                                 | 51                              |

|   | 4.1                 |                                                                                              | nce of heating time                                                                                                                                                       |                                 |

|   | 4.2                 |                                                                                              | nce of T <sub>Substrate</sub> and oxygen pressure: C-burning                                                                                                              |                                 |

|   |                     |                                                                                              | AES analysis on the efficiency of C-burning                                                                                                                               |                                 |

|   |                     | 4.2                                                                                          | .1.1 C-burning: $T_{Substrate} = 500^{\circ}\text{C}$ , $p_{O2} = 1 \cdot 10^{-5}\text{mbar}$ , $t = 30\text{mir}$                                                        | n 56                            |

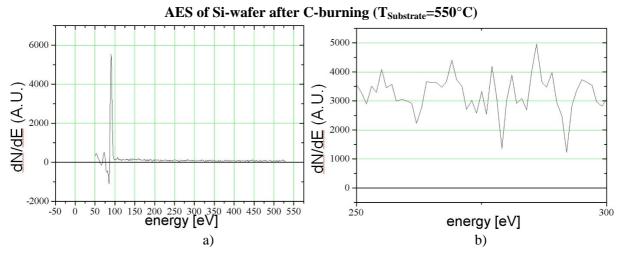

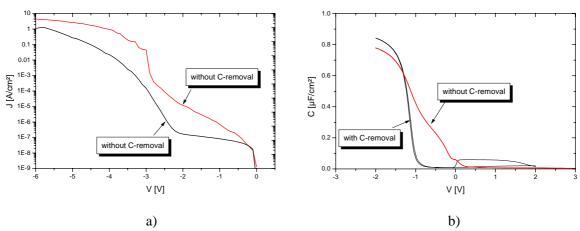

|   |                     | 4.2                                                                                          | .1.2 C-burning: $T_{Substrate} = 550^{\circ}\text{C}$ , $p_{O2} = 1 \cdot 10^{-5}\text{mbar}$ , $t = 30\text{mir}$                                                        |                                 |

|   |                     | 4.2                                                                                          | .1.3 C-burning: $T_{Substrate} = 600^{\circ}\text{C}$ , $p_{O2} = 1 \cdot 10^{-5}\text{mbar}$ , $t = 30\text{mir}$                                                        | n 57                            |

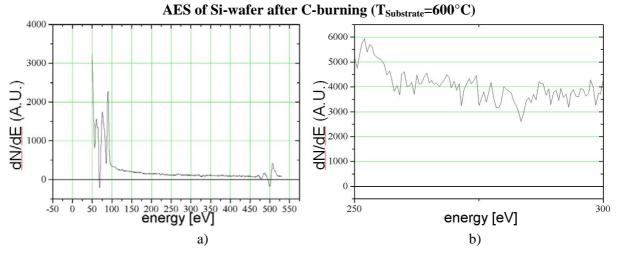

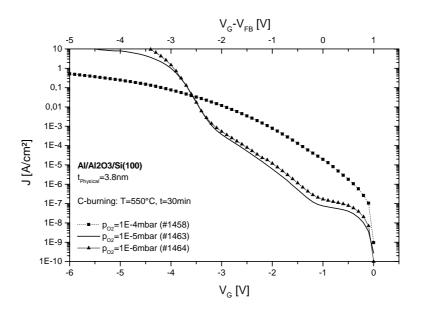

|   |                     | 4.2.2                                                                                        | Electrical investigation on the efficiency of C-burning                                                                                                                   |                                 |

|   |                     |                                                                                              |                                                                                                                                                                           |                                 |

|   |                     | 4.2.3                                                                                        | C-burning in UHV system: summary                                                                                                                                          | 59                              |

| 5 | Deno                |                                                                                              |                                                                                                                                                                           |                                 |

| 5 | -                   | sition P                                                                                     | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film                                                                                      |                                 |

| 5 | grow                | sition P<br>n by me                                                                          | rocess optimisation and characterisation of thin $Pr_2O_3$ filneans of MBD                                                                                                | ns 60                           |

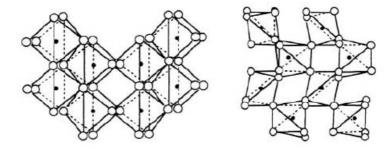

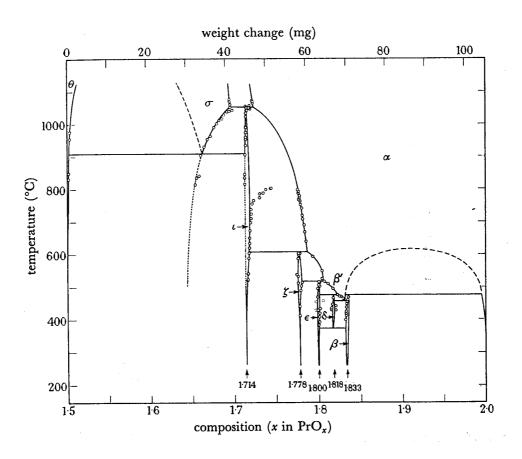

| 5 | <b>grow</b> 5.1     | sition P<br>n by me<br>Physic                                                                | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns <b>60</b>                    |

| 5 | grow                | sition P.<br>n by me<br>Physic<br>Proces                                                     | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$ ss optimisation and thermal stability of MBD-grown $Pr_2O_3$ this | ns 6060 n films62               |

| 5 | <b>grow</b> 5.1     | sition P.<br>n by me<br>Physic<br>Proces                                                     | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns 60                           |

| 5 | <b>grow</b> 5.1     | sition P. n by me Physic Proces 5.2.1                                                        | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$ ss optimisation and thermal stability of MBD-grown $Pr_2O_3$ this | ns 6060 n films6262             |

| 5 | <b>grow</b> 5.1     | rition P.  n by me  Physic  Proces  5.2.1  5.2.2                                             | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns 6060 n films626263           |

| 5 | <b>grow</b> 5.1     | Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4                                                        | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns 60                           |

| 5 | <b>grow</b> 5.1 5.2 | Physics<br>Proces<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Electric                            | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns 6060 n films62636364         |

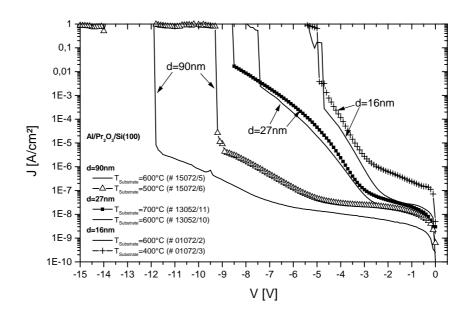

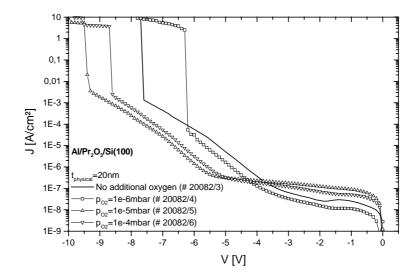

| 5 | <b>grow</b> 5.1 5.2 | Physics<br>Process<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Electric<br>5.3.1                  | rocess optimisation and characterisation of thin $Pr_2O_3$ film eans of MBD cal properties of $Pr_2O_3$                                                                   | ns 6060 n films6263636464       |

| 5 | <b>grow</b> 5.1 5.2 | Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3                                      | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film eans of MBD cal properties of Pr <sub>2</sub> O <sub>3</sub>                         | ns 60                           |

| 5 | <b>grow</b> 5.1 5.2 | sition P. n by me Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3                | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film eans of MBD cal properties of Pr <sub>2</sub> O <sub>3</sub>                         | ns 6060 n films626363646464     |

| 5 | <b>grow</b> 5.1 5.2 | Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3                                  | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film eans of MBD  cal properties of Pr <sub>2</sub> O <sub>3</sub>                        | ns 6060 n films626363646464     |

| 5 | <b>grow</b> 5.1 5.2 | Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3                                  | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film cans of MBD  cal properties of Pr <sub>2</sub> O <sub>3</sub>                        | ns 6060 n films62636364646465   |

| 5 | <b>grow</b> 5.1 5.2 | Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3 5.3 5.3                          | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film cans of MBD  cal properties of Pr <sub>2</sub> O <sub>3</sub>                        | ns 60                           |

| 5 | <b>grow</b> 5.1 5.2 | sition P n by me Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3 5.3 5.3         | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film cans of MBD  cal properties of Pr <sub>2</sub> O <sub>3</sub>                        | ns 6060 n films6263636464646565 |

| 5 | <b>grow</b> 5.1 5.2 | sition P. n by me Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3 5.3 5.3 5.3    | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film eans of MBD cal properties of Pr <sub>2</sub> O <sub>3</sub>                         | ns 6060 n films6263636464656565 |

| 5 | <b>grow</b> 5.1 5.2 | sition P n by me Physic Proces 5.2.1 5.2.2 5.2.3 5.2.4 Electri 5.3.1 5.3 5.3 5.3 5.3 5.3 5.3 | rocess optimisation and characterisation of thin Pr <sub>2</sub> O <sub>3</sub> film eans of MBD  cal properties of Pr <sub>2</sub> O <sub>3</sub>                        | ns 60                           |

|   |       | 5.3.4 Definition of UHV deposition process for Pr <sub>2</sub> O <sub>3</sub>                  | 74  |

|---|-------|------------------------------------------------------------------------------------------------|-----|

|   | 5.4   | Physical Analysis of MBD-grown Pr <sub>2</sub> O <sub>3</sub> thin films                       | 75  |

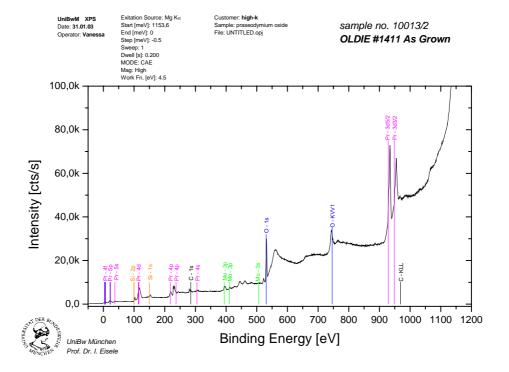

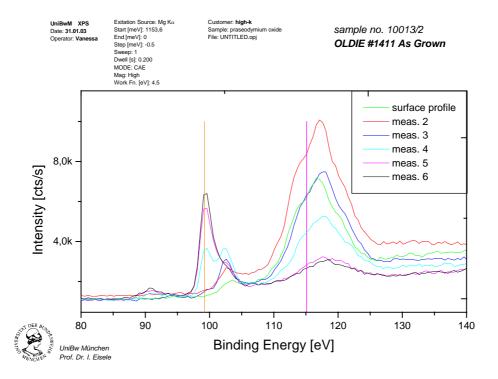

|   |       | 5.4.1 XPS                                                                                      | 75  |

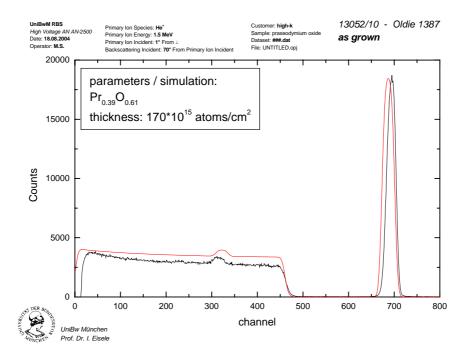

|   |       | 5.4.2 RBS                                                                                      | 76  |

|   |       | 5.4.3 TEM                                                                                      | 79  |

|   | 5.5   | Development of interface passivation process                                                   | 82  |

|   | 5.6   | Conclusion                                                                                     | 84  |

| 6 | Depo  | osition Process optimisation and characterisation of thin La <sub>2</sub> O <sub>3</sub> films | 85  |

|   | grow  | yn by means of MBD                                                                             |     |

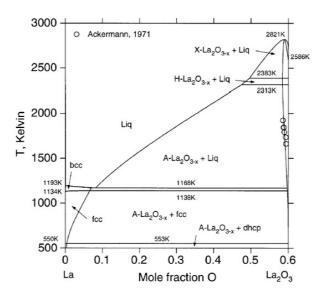

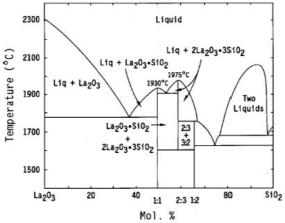

|   | 6.1   | Physical properties of La <sub>2</sub> O <sub>3</sub>                                          | 85  |

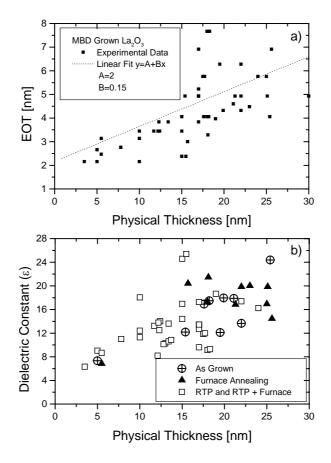

|   | 6.2   | Process optimisation and electrical characterisation of MBD-grown                              |     |

|   |       | $La_2O_3$ thin films                                                                           | 88  |

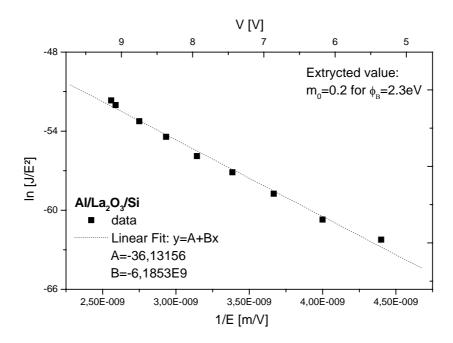

|   |       | 6.2.1 Current density vs. voltage (J-V) measurements                                           | 88  |

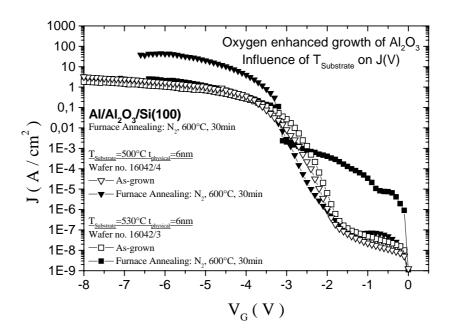

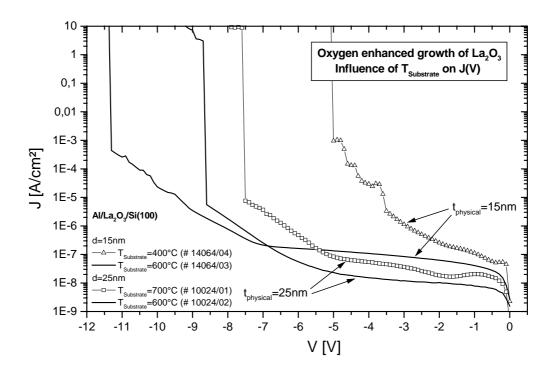

|   |       | 6.2.1.1 Influence of substrate temperature on J(V)                                             | 88  |

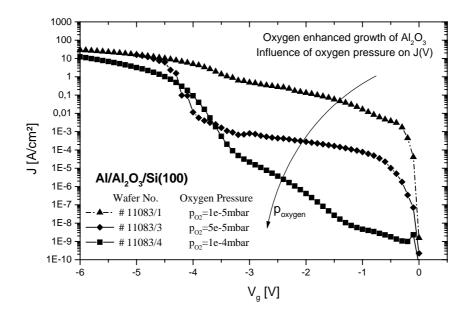

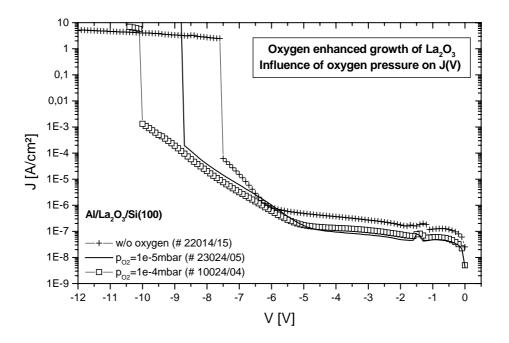

|   |       | 6.2.1.2 Influence of oxygen partial pressure on J(V)                                           | 90  |

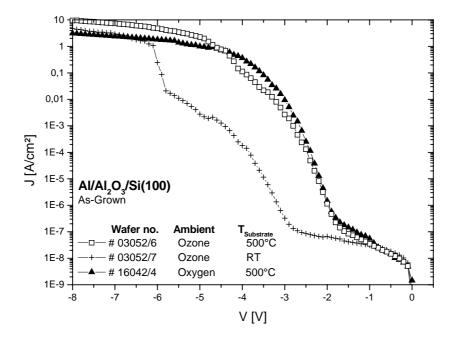

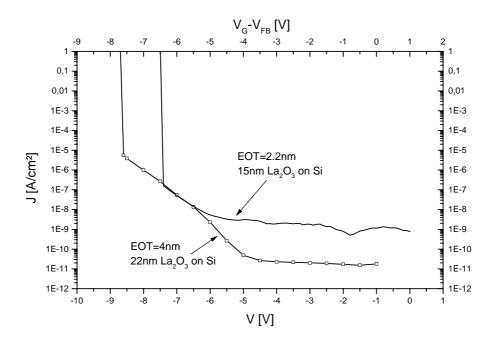

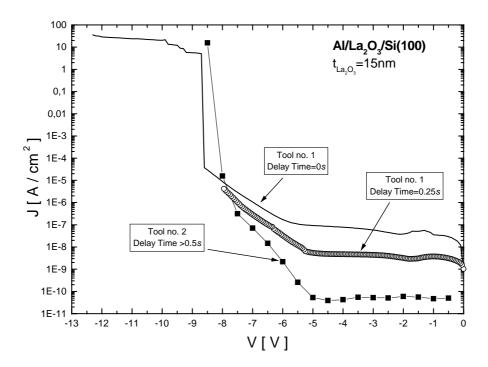

|   |       | 6.2.1.3 J(V) measurements                                                                      | 91  |

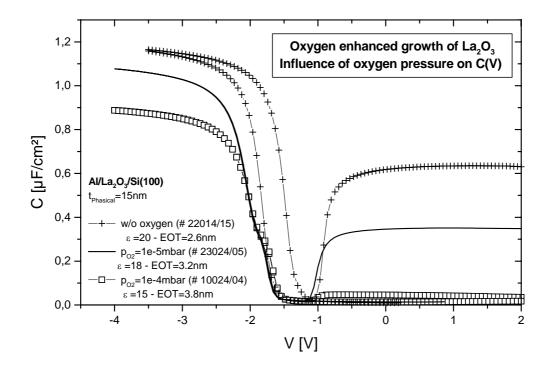

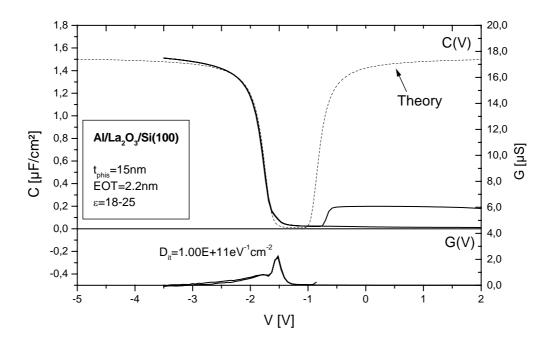

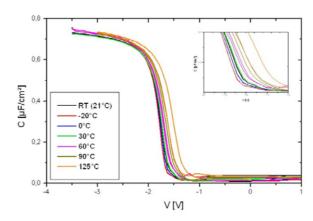

|   |       | 6.2.2 Capacitance vs. voltage (C-V) measurements                                               | 93  |

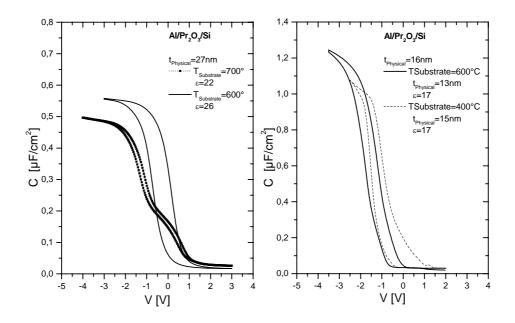

|   |       | 6.2.2.1 Influence of substrate temperature on C(V)                                             | 93  |

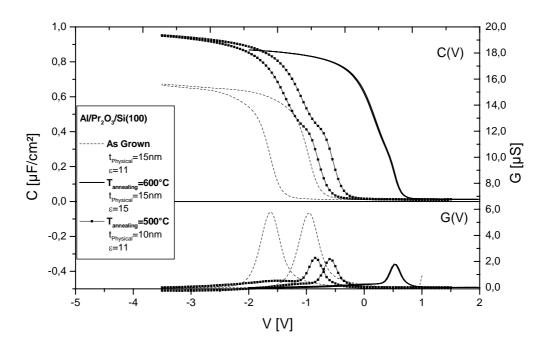

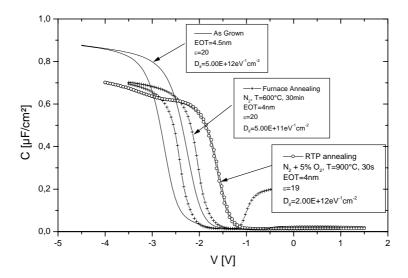

|   |       | 6.2.2.2 Influence of annealing temperature on C(V)                                             | 94  |

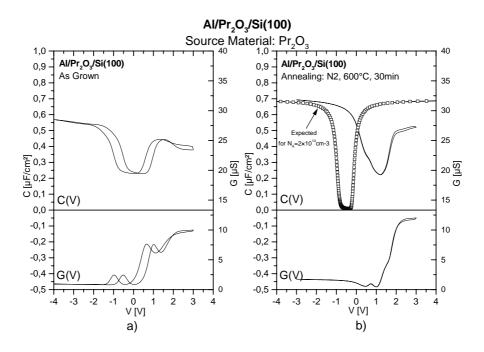

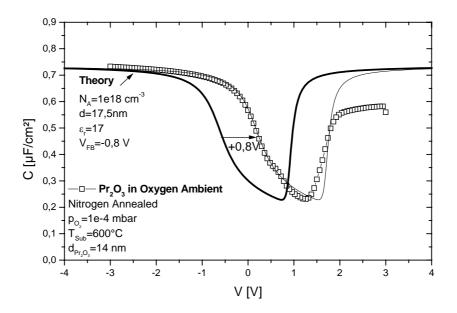

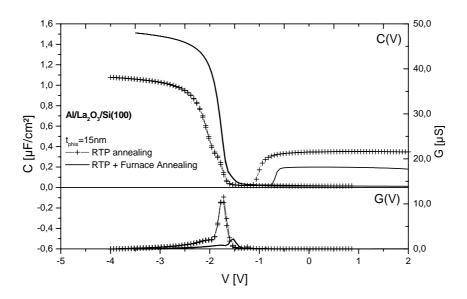

|   |       | 6.2.2.3 C(V) characterisation of MBD-grown La <sub>2</sub> O <sub>3</sub>                      | 97  |

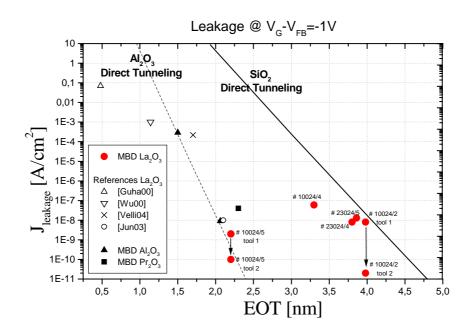

|   |       | 6.2.3 Comparison of MBD-La <sub>2</sub> O <sub>3</sub> with SiO <sub>2</sub> and Literature    | 100 |

|   |       | 6.2.4 Definition of UHV deposition process for La <sub>2</sub> O <sub>3</sub>                  | 101 |

|   | 6.3   | Physical Analysis of MBD-grown La <sub>2</sub> O <sub>3</sub> thin films                       | 101 |

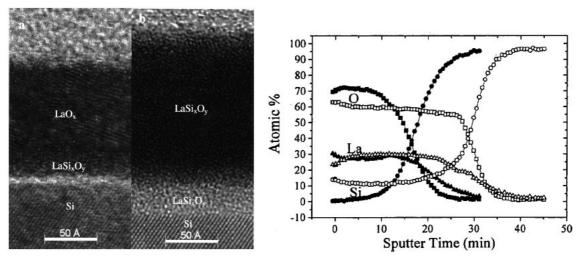

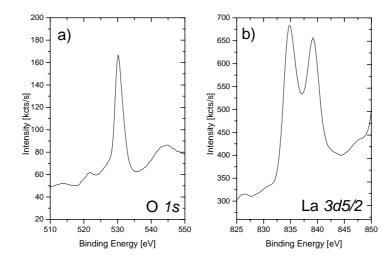

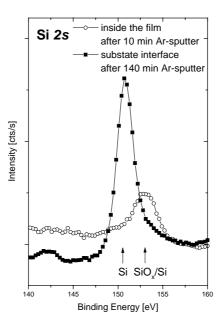

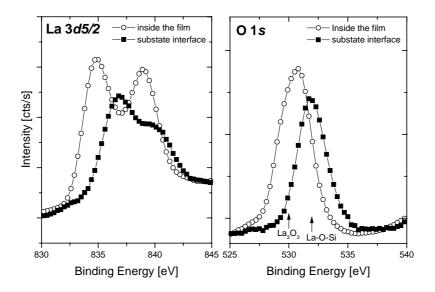

|   |       | 6.3.1 XPS                                                                                      | 101 |

|   |       | 6.3.2 RBS                                                                                      | 104 |

|   |       | 6.3.3 TEM                                                                                      | 105 |

|   | 6.4   | Interface engineering                                                                          | 105 |

|   | 6.5   | Conclusion                                                                                     | 107 |

| 7 | Cone  | clusion and Outlook                                                                            | 108 |

|   | Bibli | iography                                                                                       | 110 |

|   | Publ  | lication                                                                                       | 115 |

|   | Ackı  | nowledgement                                                                                   | 116 |

## **Chapter 1**

## Introduction

## 1.1. Dimension Shrinking in CMOS Technology

The semiconductors industry is continuously prospering since the early 1970s and it is without any doubt the main driving force for the new information age. The main reason for this sustained growth is the decrease in device feature size which enables improved functionality at a reduced cost.

In the last thirty years the dimension shrinking and the performance improvement of the electrical devices have been predicted very well by the Semiconductors Industry Association (SIA) in the International Technology Roadmap for Semiconductors (ITRS), where a 15-year outlook on the major trends of the semiconductor industry is given [ITSR].

In 1975 Gordon Moore, the founder of Intel Inc., build the fundament of the ITRS-roadmap. In his "law" G. Moore predicted that the number of transistor on a chip would quadruple every 36 months [Moore75]. As such, the semiconductor industry could gain 30% more every year. He updates his prediction in 1985 reducing the cycle of quadrupling to 24 months. It is very fascinating to see how the device-scaling has strictly followed this law for the last thirty years. The future technology generation predicted by the ITRS in its 2004 version are shown in Table 1-1.

According to the ITRS the expected physical gate length will be 53nm in 2005. This is a very important parameter as the shrinking of the transistor gate length (L) reduces the carriers travelling time between source and drain, hereby improving the device speed.

The physical sizes of the devices are miniaturised with the same factor S according the scaling method. For this reason the shortening of the transistor channel length leads to the corresponding scaling of gate area and gate oxide thickness in order to maintain the same transistor parameters such as threshold voltage and capacitance [Sze81, Section 8.5].

After thirty years now the traditional scaling is indeed approaching the fundamentals limits of the materials constituting the building blocks of the CMOS process [ITRS, Buch99, Wong02].

One of the bigger hurdles in the traditional process shrinking approach is the gate insulator. To be able to follow the dimension shrinking according to the ITRS, the SiO<sub>2</sub> film thickness should become below 1nm within the next three years. This thickness corresponds to few atomic layers, which means that the direct tunnel leakage current through the insulator will increase. The high leakage current and the inadequate reliability for a SiO<sub>2</sub> layer of less than 1.5nm thickness require a replacement for SiO<sub>2</sub>. Therefore new materials have to be introduced into the basic CMOS structure to replace the existing ones to further extend device scaling and the reduction of the production costs.

| Year of Production                                                                                       | 2003    | 2004    | 2005    | 2006    | 2007    | 2008    | 2009    |

|----------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Technology Node                                                                                          | 1       | hp90    | ì       | )       | hp65    |         | 1       |

| DRAM ½ Pitch (nm)                                                                                        | 100     | .90     | 80      | 70      | 65      | 57      | 50      |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                       | 120     | 107     | 95      | 85      | 76      | 67      | 60      |

| MPU/ASIC ½ Pitch (nm)                                                                                    | 107     | 90      | 80      | 70      | 65      | 57      | 50      |

| MPU Printed Gate Length (nm)                                                                             | 65      | 53      | 45      | 40      | 35      | 32      | 28      |

| MPU Physical Gate Length (nm)                                                                            | 45      | 37      | 32      | 28      | 25      | 22      | 20      |

| Physical gate length low standby power (LSTP) (nm) [1]                                                   | 75      | 65      | 53      | 45      | 37      | 32      | 28      |

| EOT: equivalent oxide thickness (physical) for LSTP (nm) [2]                                             | 2.2     | 2.1     | 2.1     | 1.9     | 1.6     | 1.5     | 1.4     |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                  | 0.8     | 0.8     | 0.7     | 0.7     | 0.7     | 0.4     | 0.4     |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                              | 3       | 2.9     | 2.8     | 2.6     | 2.3     | 1.9     | 1.8     |

| Nominal gate leakage current density limit (at 25°C) (A/cm²)<br>[5]                                      | 4.4E-03 | 5.1E-03 | 9.4E-03 | 1.5E-02 | 2.3E-02 | 3.1E-02 | 4.8E-02 |

| Nominal LSTP power supply voltage (Vád) (V) [6]                                                          | 1.2     | 1.2     | 1.2     | 1.2     | 1.1     | 1.1     | 1.1     |

| Saturation threshold voltage (V) [7]                                                                     | 0.50    | 0.50    | 0.51    | 0.52    | 0.50    | 0.47    | 0.47    |

| Nominal LSTP NMOS sub-threshold leakage current, I <sub>sd,leak</sub> (at 25°C) (μΑ/μm) [8]              | 1.0E-05 | 1.0E-05 | 1.5E-05 | 2.0E-05 | 2.5E-05 | 3.0E-05 | 4.0E-05 |

| Nominal LSTP NMOS saturation drive current, $I_{d,sat}$<br>(at $V_{dd}$ , at 25°C) ( $\mu A/\mu m$ ) [9] | 410     | 440     | 470     | 510     | 510     | 670     | 700     |

| Required "mobility/transconductance improvement" factor [10]                                             | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     | 1.3     | 1.3     |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) (0-1) [11]                  | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     |

**Table 1-1** Low Standby Power Technology Requirements [ITRS, table 48c]

## 1.2. Alternative gate dielectrics

The traditional scaling, which has been the driving force of the semiconductor industry for the last 30 years, is reaching the fundamental limits of the standard materials for planar CMOS devices. New materials have to be introduced into the basic CMOS structure.

The most critical point for the shrinking to the 100nm-feature-size is the introduction of an high dielectric constant (high-k) material as alternative gate oxide. Among all materials for MOS devices, the gate oxide remains one of the most critical since it plays a fundamental role in "field effect" control. Thermally grown oxide (SiO<sub>2</sub>) has been used as gate dielectric since the introduction of the MOSFET devices. The natural choice of silicon dioxide is due to its very good compatibility with silicon substrate, grow-process simplicity on it and nearly perfect insulator properties. However, the phase-out of SiO<sub>2</sub> is needed as early as the 100nm node due to the high leakage currents and inadequate reliability for SiO<sub>2</sub> dielectric layer of less than 1.5nm thickness [ITRS].

Extensive research is under way to replace the traditional silicon dioxide /dual –doped polysilicon gate stack process with high-k gate dielectric and new gate electrode materials.

In general the capacitance (C) of a MOS capacitor is given as:

$$C = \varepsilon_0 \varepsilon_r \frac{A}{t_{ox}} = \varepsilon_0 \varepsilon_{SiO_2} \frac{A}{t_{SiO_2}}$$

where  $\varepsilon_r$  is the relative permittivity of the gate oxide (dielectric constant),  $\varepsilon_0$  is the permittivity of vacuum, A the capacitor area, and  $t_{ox}$  the gate oxide physical thickness. By assuming the same capacitance is achieved using SiO<sub>2</sub> as dielectric, the Equivalent Oxide Thickness (EOT) is given by:

$$EOT = t_{ox} \frac{\mathcal{E}_{SiO_2}}{\mathcal{E}}$$

which means that with an high dielectric constant ( $\epsilon$ ) a thick gate dielectric layer gives an appropriate capacitance value equal to that of an equivalent thin silicon dioxide.

The relative permittivity of a material is typically given by  $\varepsilon_r$  and the relation between k and  $\varepsilon$  depends on the choice of units. Anyway, it is always the case that k is proportional to  $\varepsilon$  and for this reason in this thesis the definition  $k = \varepsilon$  is used.

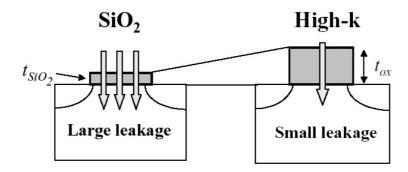

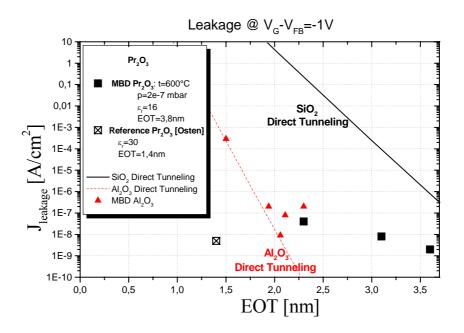

The advantage of using a thick high-k gate oxide is the elimination of direct tunneling, as illustrated in figure 1.1. Therefore high-k materials are excellent candidates for replacements of the traditional  $SiO_2$  gate oxide.

**Figure 1.1** Suppression of the direct tunnel leakage current through the gate insulator by introducing alternative gate oxides having a high dielectric constant (high-k).

The evolving near-term solutions for the gate dielectric problem are materials like oxynitride,  $Si_3N_4$  and  $Al_2O_3$ . These dielectrics have relatively low  $\varepsilon$  value compared with others high-k materials but they are very well studied and can be easily integrated into the conventional CMOS process. In general materials having dielectric constant around 10 are suggested for short term and materials having  $\varepsilon$ >20 for long term solution.

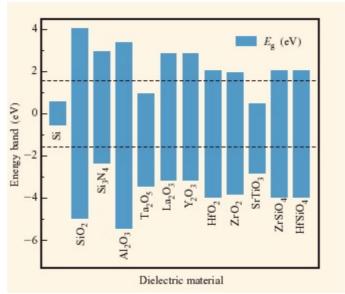

The dielectric constant  $\varepsilon$  is not the only parameter to be taken into consideration when choosing an alternative gate oxide. A crucial point for the control of leakage current in MOS devices are the band-gap of the dielectric and band alignment with respect to silicon, while high barrier height favors low leakage current. Bandgaps of 4-5eV with a barrier height of more than 1eV is necessary to limit thermionic emission and Fowler-Nordheim tunneling [ITRS, Sze81]. Furthermore, negligible trap densities in dielectric layers are required to suppress Frenkle-Poole tunneling [Frenk38]. Finally thermal stability with respect to silicon is another important factor to be taken into account since high temperature annealing are typically employed in standard CMOS processes.

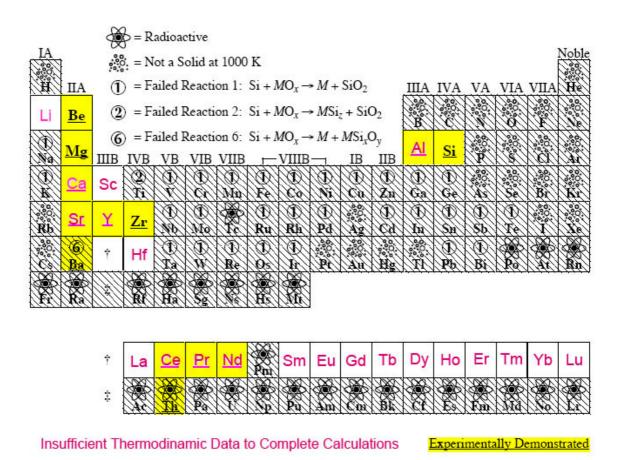

The most comprehensive study on the thermal stability of binary oxide with respect to silicon at 1000K has been published by Hubbard and Schlom [Hubba96]. In this work they evaluated the free energies of reactions for producing known oxide or silicate products. Metal oxide were characterized as thermodynamically stable or unstable in contact with

silicon. All binary oxides are thermodynamically unstable with silicon at 1000K except the Li<sub>2</sub>O, most of the alkaline earth oxide (BeO, MgO, CaO, and SrO), the column IIIB oxide (Sc<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub>), ThO<sub>2</sub>, UO<sub>2</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>. Among these material, BeO, MgO, CaO, SrO, Y<sub>2</sub>O<sub>2</sub>, Pr<sub>2</sub>O<sub>3</sub>, Nd<sub>2</sub>O<sub>3</sub>, ThO<sub>2</sub>, ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> have been studied and appear to be free of reaction layer on silicon. There is sufficient data to conclude that BeO, MgO and ZrO<sub>2</sub> are stable, but insufficient data for the others. It is also possible to have ternary or higher multi-component-oxides for direct integration with silicon, i.e., combination of binary oxides that are all thermodynamically compatible with silicon, e.g. ZrSiO<sub>4</sub>, LaAlO<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>-ZrO<sub>2</sub>, MgAlO<sub>4</sub>, etc. However, for those high-k dielectrics that are unstable in direct contact with silicon, an engineered interfacial layer will be required in order to take advantage of their potential dielectric characteristics.

A summary of which elements M have an oxide  $(M_{ox})$  that may be thermodynamically stable in contact with silicon at 1000K is shown in figure 1.2.

**Figure 1.2** Summary of which elements M have an oxide (Mox) that may be thermodynamically stable in contact with silicon at 1000K, based on [Hubba96]. Elements M having no thermodynamically-stable or potentially thermodynamically-stable oxide (Mox) are shaded and the reason for their elimination is given. Also shown are the elements M having an oxide Mox that has been experimentally demonstrated to be stable in direct contact with silicon. Performing the thermodynamic analysis at room temperature rather than 1000K does not alter the conclusion of the thermodynamic stability analysis for oxides Mox of any of the elements [Schlom].

A list of high-k materials is reported in table 1-2 and the band-gap and band alignment for some of the systems is illustrated in figure 1.3.

Until now, none of the above materials has emerged as the most likely candidates to meet all the complex requirements associated with processing, device performances and reliability. Research focuses on the individuation of the alternative gate oxide considering different growth techniques, their optimization for the deposition of high-k materials and studying the corresponding gate stack system: high-k dielectric, interfacial layers, gate electrode and compatibility with CMOS process flow.

**Table 1-2** Selected material and electrical properties of high-k dielectric

| Material                | 3       | Band Gap | ΔΕС  | Crystal Structure                      |

|-------------------------|---------|----------|------|----------------------------------------|

|                         |         | [eV]     | [eV] | •                                      |

| Binary Oxides           |         |          |      |                                        |

| $SiO_2$                 | 3,9     | 9        | 3,5  | Amorphous                              |

| $Si_3N_4$               | 7       | 5.3      | 2.4  | Amorphous                              |

| $Al_2O_3$               | 9       | 8.7      | 2.8  | Amorphous                              |

| $Y_2O_3$                | 15      | 6        | 2.3  | Cubic                                  |

|                         |         |          |      | amorphous upto 850°C anneal            |

| $La_2O_3$               | 20-30   | 6        | 2.3  | Hexagonal, cubic, amorphous            |

| $Ta_2O_5$               | 25      | 4.4      | < 1  | Orthorhombic                           |

| $TiO_2$                 | 80      | 3.5      | 1.2  | Tetragonal (rutile, anatase)           |

| $HfO_2$                 | 20      | 6        | 1.5  | Monoclinic, tetragonal, cubic          |

| $ZrO_2$                 | 12-25   | 5,8      | 1.4  | Monoclinic, tetragonal, cubic          |

| $Er_2O_3$               | 7       |          |      | -                                      |

| $Pr_2O_3$               | 31      | 2,5-3,9  |      | Crystalline with interfacial amorphous |

|                         |         |          |      | layer Pr-Si-O                          |

| $Gd_2O_3$               | 14      |          |      | amorphous upto 850°C anneal            |

|                         |         |          |      |                                        |

| Silicates               |         |          |      |                                        |

| $3(HfO2)_x(SiO2)_{1-x}$ | 11      | 6        | 1.5  | Amorphous upto 800°C                   |

| $3(ZrO2)_x(SiO2)_{1-x}$ | 10 - 12 | 6        | 1.5  | Amorphous upto 800°C                   |

**Figure 1.3** Band-gap and band alignment of high-k gate dielectrics with respect to silicon. The dashed lines represents 1eV above/below the conduction/valence band. After [Wong02, figure 2]

### 1.3. Scope of the present research and thesis outline

This research thesis focuses on the proposition and investigation of three alternative gate oxide systems, which are aluminium-, praseodymium and lanthanum oxide ( $Al_2O_3$ ,  $Pr_2O_3$  and  $La_2O_3$ , respectively). The choice of these system was based on the main criteria for high-k dielectrics, i.e. thermal stability, band-gap and band alignment as well as interface properties with silicon substrate.

The growth process was optimised in UHV-system by molecular beam deposition (MBD) for the three systems under consideration. The high-k gate dielectric stacks have been studied using physical and electrical characterisation techniques to gain a better understanding of important factors associated with alternative gate dielectrics from both a theoretical and experimental points of view.

Detailed electrical characterisation has been performed on metal-oxide-semiconductor (MOS) capacitors. The material characterisation is concentrated on understanding the physical and chemical properties of the gate stacks on an atomic or near-atomic scale.

In the first part of the thesis aluminium oxide is investigated in order to have a reliable reference. Aluminium oxide ( $Al_2O_3$ ) is one of the first systems which have been studied to replace silicon dioxide as gate dielectric. Its large barrier height (8.7eV), large band offset with respect to silicon and a dielectric constant ( $\epsilon$ =8-10) double than  $SiO_2$  makes of  $Al_2O_3$  an interesting candidate for a short term solution of the gate oxide problem. Moreover aluminium oxide is a very stable and robust material, extensively studied for many application in microelectronics and it can be easily integrated into the conventional CMOS process. The basic properties of  $Al_2O_3$  films grown on silicon substrate are well understood. For this reason alumina is a good reference material to investigate on new alternative gate oxide.

Very promising candidates for alternative gate dielectric are the lanthanide oxides (rare earth oxides). In particular praseodymium oxide and lanthanum oxide have attracted the attention because of their dielectric constant (20-30) and thermal stability on silicon substrate until 1000K.

The first rare earth oxide investigated in this thesis is praseodymium oxide. The possibility to grow  $Pr_2O_3$  thin films on silicon substrate by molecular beam deposition (MBD) was already reported in literature and the promising electrical results of the MBD-grown layer made of this system the ideal candidate to optimise the deposition process of lanthanide oxides in UHV.

The second investigated rare earth oxide is the lanthanum oxide. The advantage of  $La_2O_3$  compared to the others lanthanide oxides are the higher band-gap and band-offset with respect to silicon and the stronger resistance to crystallisation.

The properties of thin lanthanum oxide films as dielectric system for microelectronic application are not yet completely known and intensive research is running to find out if this dielectric will cover all the requirement needed for the new gate oxide material. In particular the major drawback of lanthanum oxide, as all others rare earth metal oxide, is given by its high sensibility to humidity, which leads to degradation of the dielectric film. This thesis will try to give an answer to the open questions and will profile the direction for future investigations.

The experimental techniques involved in the deposition process and characterisation of the high-k materials are presented in Chapter 2.

The optimisation of the MBD process and the characterisation of the grown films is illustrated for Al<sub>2</sub>O<sub>3</sub>, Pr<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub> respectively in chapters 3, 5 and 6 while chapter 4 is about the investigation on the interface between dielectric and silicon substrate (interface engineering) and its influence of the electrical properties of the gate stacks.

Finally, conclusion and results emerging from the studies of the alternative gate oxide considered in this thesis are summarised in chapter 7 and a direction for future investigation is proposed.

## **Chapter 2**

## **Deposition and Characterisation Methodologies**

The Metal-Insulator-Semiconductor (MIS) diode is the most useful device in the study of the electrical properties of the gate dielectric material and the quality of the interface between the silicon substrate and the gate oxide. In general MOS systems have been extensively investigated because they are directly related to most planar devices and integrated circuits. A comprehensive and in-depth study of the Si-SiO<sub>2</sub> MOS diode can be found in *MOS Physics and Technology* by Nicollian and Brews [Nico82] and in *Physics of Semiconductor Device* by Sze [Sze81]

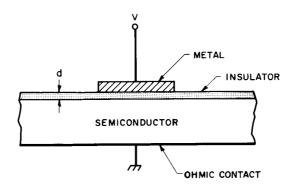

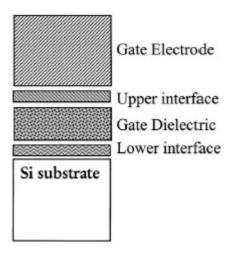

The MIS- structure is illustrated in figure 2.1. A metal plate (gate) is separated from the semiconductor substrate by a thin insulating layer, where d is the thickness of the insulator and V is the applied voltage on the metal field plate.

Figure 2.1 Cross section of a Metal-Insulator-Semiconductor (MIS) diode

In this study, low doped silicon wafers (p̄, <100>) have been used as substrate material to fabricate MIS structures. First of all the wafers were wet-cleaned using the recipe indicated in table 2-1. After that they were loaded in an Ultra-High-Vacuum (UHV) reactor where alternative gate oxides were grown by Molecular Beam Deposition (MBD).

The process flow for the preparation of MIS capacitors can be summarised as follow:

- Si-substrate wet cleaning

- Loading in UHV

- Gate oxide deposition by MBD

- Post-growth annealing (furnace annealing or RTP)

- Aluminium-electrode evaporation

A clear understanding of various physical phenomena occurring at silicon surface was for a long time limited by the fact that it is almost impossible to properly characterise surface and interface in the ambient atmosphere. Clean surfaces are very reactive towards gas molecules and other particles and therefore change rapidly.

A proper study of surfaces and interfaces became possible in the last decades due to the development of Ultra-High-Vacuum (UHV) techniques. In this chapter we describe a number of experimental techniques intensively used for the preparation and characterisation of gate oxide thin films. Such techniques are employed to investigate the physical properties of MBD-grown aluminium-, praseodymium- and lanthanum oxide.

| Process Step | Solution                         | <b>Process Conditions</b> |

|--------------|----------------------------------|---------------------------|

| RCA 1        | 5 H <sub>2</sub> O               | 15 min                    |

|              | 1 NH <sub>3</sub> (25%)          | 50°C                      |

|              | $1 \text{ H}_2\text{O}_2 (30\%)$ |                           |

| washing      | DI-Water                         |                           |

| RCA 2        | 5 H <sub>2</sub> O               | 15 min                    |

|              | 1 NH <sub>3</sub> (25%)          | 50°C                      |

|              | $1 \text{ H}_2\text{O}_2 (30\%)$ |                           |

| HF-last      | $100 \text{ H}_2\text{O}$        | 30 s                      |

|              | 1 HF                             | Room Temperature          |

|              |                                  | Without light             |

Table 2-1 RCA cleaning for silicon wafers

### 2.1. Molecular Beam Deposition

Molecular Beam Epitaxy (MBE) is a technique developed in the early 1970s to grow high-purity thin epitaxial layers on crystalline substrate. The word epitaxy derives from the Greek "epi" meaning surface and "taxia" meaning arrangement and refers to the process of growing complex structures with an atom-by-atom arrangement on a substrate surface which is maintained at elevate temperature in ultrahigh vacuum.

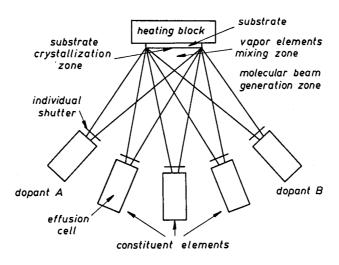

A schematic illustration of the essential part of an MBE system is shown in fig. 2.2. The source materials are placed in evaporation cells and reactive gas can be introduced in the process chamber by gas-inlets. Moreover, the substrate is heated to the needed temperature and, if necessary, rotated to improve the film homogeneity.

**Figure 2.2** Schematic illustration of the essential part of an MBE system. After [Herm89]

The epitaxial layers are formed by reaction between the atomic beams of the constituent materials and the surface atoms of the substrate. MBE is a very flexible technique since it allows to modify the composition of the grown epitaxial layer simply changing the arrival rates of the constituent elements and dopants, which depend on the evaporation rates of the respective sources. An exhaustive description of MBE process and application can be found in [Park85, Herm89].

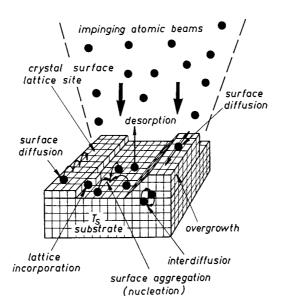

To describe the epitaxial growth, normally the MBE system is divided into three zones because of the different physical reactions taking place in an MBE [Herm89]. In the first zone the atomic and molecular beams are generated. In the second one beams created by different sources get in contact forming a special gas mixture. In the third zone the gas mixture reach the substrate and the epitaxial growth take place. The principal physical processes that play a role in MBE growth are listed below and illustrated in figure 2.3:

- i) adsorption of the atoms and molecules impinging on the substrate;

- ii) surface migration and dissociation of the adsorbed molecules;

- iii) incorporation of the atoms into the crystal lattice of the substrate;

- iv) thermal desorption of the species not incorporated into the crystal lattice.

**Figure 2.3** Schematic illustration of the surface processes occurring during film growth by MBE (after M.A. Herman and H. Sitter [Herm89])

Depending on the exchanged electron between the impinging atoms and the substrate ones, the adsorption process can be divided into physisorption and chemisorption. In physisorption (the name stays for physical adsorption) there is no electron exchanges between the adsorbate (gas atoms) and the adsorbent (substrate). Physisorption presents small activation energy ( $0 < E_A < 1 \text{ eV}$ ) and the reactive forces are van der Waals type [Neu98]. When electrons are exchanged between adsorbate and adsorbent, than the adsorption is called chemisorption and a chemical reaction characterised by high bonding energies takes place. After a certain time the atoms or molecules that have not reacted with the substrate will be let free by a thermal process called desorption that strongly depends

on the substrate temperature. The substrate temperature has also an high influence on the crystal quality of the grown layers: in general the grown layer is amorphous for low substrate temperature and polycrystalline or crystalline when the substrate is maintained at high temperature. The "low-" and "high- temperature" definition depends on the materials and on deposition parameters like the flux-rate of elements to be grown. Typically, very low constituent flux rate are necessary (Å/s) in order to assure the surface migration of the impinging species on the growing surface.

The low growth rate typical for conventional MBE techniques coupled with the necessity of very low unintentional impurity levels in the epitaxial layer lead to the conclusion that MBE growth should be carried out in an UHV environment. If the residual gas pressure in the process chamber is not low enough, the beam molecules coming from the cells may encounter the residual gas molecules during their way to the substrate. In this case the scattering processes would degrade the beam nature of the mass flow. The highest admissible value of the residual gas pressure is determined by the condition that the mean free path L of the molecules of the reactant beam penetrating the environment of the residual gas has to be larger than the distance from the beam source to the substrate surface. The mean free path is described as [Herm89]

$$L = \frac{1}{\sqrt{2}\pi nd^2}$$

where d is the molecular diameter and n the concentration of the gas molecules in the vacuum. The concentration of the gas molecules is function of pressure p and temperature T and is given by the formula [Herm89]:

$$n = \frac{p}{k_B T}$$

Another way to define the maximal residual gas pressure is to compare the time necessary to deposit a monolayer of the reactant beam and of the residual gas on the substrate: for a sufficient clean epilayer it is necessary that the relation between the deposition time of one monolayer of the reactive beam  $t_1(b)$  and the deposition time of the residual gas vapor  $t_1(v)$  is at least  $t_1(b)=10^{-5}t_1(v)$  [Herm89].

Assuming that the residual gas in the vacuum reactor consist only of nitrogen molecules the calculated  $t_1(v)$  would be  $t_1(v)=10^{19}(5.74\cdot10^{22}p_i)^{-1}$ . Solving the equation by saying that  $t_1(v)$  has to be larger than or equal to  $10^5$ s, it follows that the pressure of the residual gas in the vacuum reactor must be smaller or equal to  $1.7\cdot10^{-9}$ Pa.

Strictly speaking, the term "MBE" should be only used for epitaxial crystal growth on single crystalline substrate using a molecular beam. Therefore in this work the term "Molecular Beam Deposition" (MBD) is here used instead of MBE, since deposition of amorphous insulator materials on silicon substrate is the argument treated in this thesis work.

#### 2.1.1 MBD of Alternative Gate Dielectrics

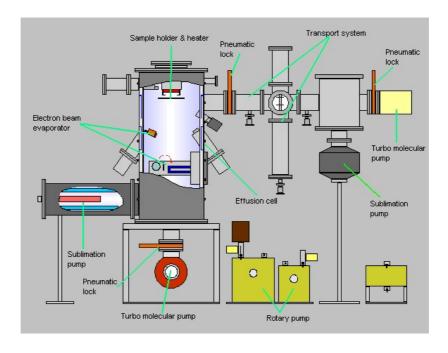

The development of the growth-processes of alternative gate oxide films on silicon substrates was carried out in an UHV-reactor (figure 2.4) by Molecular Beam Deposition. A detailed description of the specific system used in this thesis is argument of the PhD

thesis [Neu98]. This UHV-system has a residual gases pressure in the process chamber smaller than  $1 \cdot 10^{-8}$  mbar, thus the contamination of the silicon substrate due to residual gas could be neglected.

The UHV-reactor is equipped with an effusion cell which was used for the evaporation of aluminium and an electron beam evaporation system (e-beam) for the evaporation of praseodymium- and lanthanum-oxide.

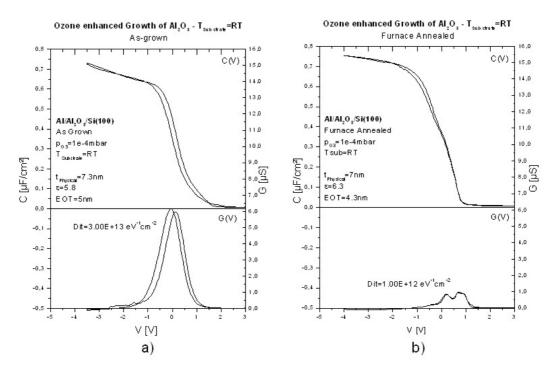

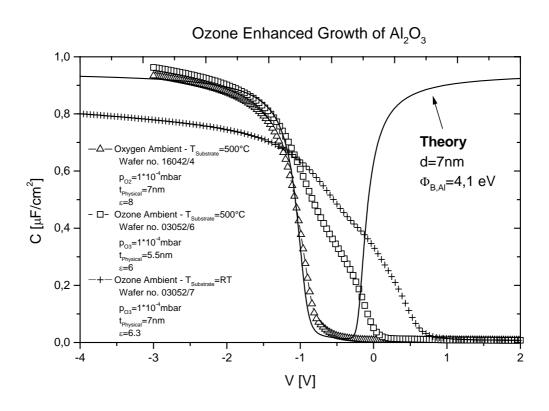

Aluminium-oxide layers were grown by exposing the silicon wafer to aluminium molecular beams in an oxidising ambient. The reactive gases (oxygen or ozone) were introduced in the chamber by a gas inlet and the working pressure was sufficiently high to allow the deposition of stoichiometric  $Al_2O_3$ -film ( $1\cdot10^{-4}$ mbar). The measured  $Al_2O_3$ -growth rate was around 0.5nm/min. A substrate temperature of 500°C was chosen in order to deposit an amorphous layer.

Praseodymium and lanthanum oxide require an electron-beam source to reach the evaporation temperature. Commercially available  $Pr_2O_3$  (99.996%) and  $La_2O_3$  powder (99.99%) were used as source material. When necessary oxygen reactive gas was introduced in the chamber by a gas inlet. The substrate temperature during deposition was set to the range of  $500^{\circ}\text{C}$ - $700^{\circ}\text{C}$  and the typical deposition rates were 1-3nm/min.

After deposition the wafers were transferred to a furnace or RTP-oven for post-growth annealing.

To electrically characterise the deposited films MOS capacitors were defined: aluminium electrodes were thermally evaporated on the gate oxide layer using a shadow mask and on the back-side of the wafer.

**Figure 2.4** UHV-reactor used for Molecular Beam Deposition of alternative gate oxide.

#### 2.2. Electrical Characterisation Methods

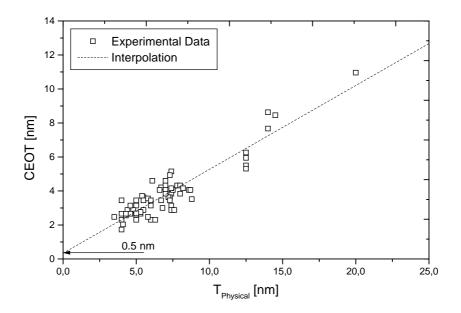

Electrical characterisation of the metal-oxide-semiconductor (MOS) capacitors is used to extract the electrical parameters from various gate dielectrics. The principal characterisation methods are capacitance vs. voltage C(V), current vs. voltage I(V) and conductance G(V) measurements. From these measurements the Equivalent Oxide Thickness (EOT), Capacitance Equivalent Oxide Thickness (CEOT), interface trap density  $(D_{it})$  and current density at a given bias (J) are calculated. In this section, a brief review of the electrical characterisation techniques is given.

#### 2.2.1 C(V) measurements

Capacitance vs. voltage characterisation of the MOS capacitors represents a well established and rapid method to determine important gate-dielectric parameters. The classical C-V theory has been widely reported by Nicollian and Brews [Nico82] for thick gate dielectrics. As the oxide thickness decreases the standard C-V methods has to be re-elaborated taking into account effects like substrate quantum mechanical effects and polysilicon gate-depletion. The influence of these factors in the extraction of the electrical parameters increases for very thin dielectric.

Quantum mechanics says that the density of inversion electrons reaches a peak at approximately 1 nm below the silicon surface. Hereby the gate capacitance and the inversion charge are reduced which results in an apparent increase in the equivalent oxide thickness on the order of 0.25 to 0.3 nm. Similarly depletion effects occur when the gate electrode is given by polysilicon: a finite polysilicon doping density requires a finite depleted thickness of polysilicon to accommodate the surface field. For this reason the electrically determined thickness is larger than the real physical thickness of the gate dielectric. The percentage of gate-capacitance attenuation becomes more significant as the oxide thickness is scaled down [Taur02].

A schematic overview of the various region associated with the gate stack of a MIS capacitor is reported in figure 2.5, where the interface region are highlighted.

Figure 2.5 Schematic illustration of the important region of a MIS capacitors

Different modelling programs have been developed to extract the dielectric thickness from the experimental data: NCSU's CVC, UC Berkeley's QMCV and IBM's TQM are few of them. In this work, North Carolina State University's CVC has been used as standard

modelling tool because of its accurate and fast results. The physical oxide thickness and device parameters such as the substrate doping, flatband voltage and polysilicon gate doping are calculating by matching the experimental C(V) data to a physics-based theoretical model [Ahme00]. Using these parameters, the analysis program provide first-order models for polysilicon depletion and quantum mechanical effects using a least-squares error algorithm and returns the best-fit values of these parameters for a given C(V) characteristic.

#### 2.2.1.1. C(V) and G(V) data acquisition and analysis

Important information on the properties and quality of the gate dielectric material can be extracted from C(V) and G(V) measurements on MOS devices.

C(V) characteristics allow the extraction of the equivalent oxide thickness EOT of the gate oxide. Depending on the extraction method used two oxide thickness values are indicated: one is the capacitance equivalent oxide thickness (CEOT), calculated from the capacitance measured in strong accumulation, and the other is the equivalent oxide thickness (EOT), which is the value after QM correction obtained using the NCSU CVC program [Haus96]. The presence of charge in the dielectric layer can be extracted by considering stretch-out, hysteresis or shift of the flat band voltage shift (V<sub>FB</sub>) in the C(V) characteristics [Nico02, Baum03]

The study of the interface between gate oxide and silicon substrate is done by considering the equivalent parallel conductance G(V). Theory and procedure to extract the interface state density  $D_{it}$  from G(V) measurements is argument of section 2.2.2 of this chapter.

The capacitance vs. voltage measurements were performed on MOS capacitors using a shielded 4-point-prober in combination with a HP 4275A LCR Meter. The low-level signal frequency was set to 20 kHz. Capacitance and equivalent parallel conductance were measured ramping a voltage range between –3 V and +2 V. Prior to data acquisition, an open and short-circuit correction was performed.

The MOS capacitor can be approximated by three-element model consisting of a capacitance, C, a conductance, G, and a series resistance, r<sub>S</sub>. Series resistance can cause a serious error in the extraction of interfacial properties. For this reason, the measured capacitance and conductance values for the MOS capacitors have been corrected following the methods developed by Nicollian and Brews [Nico82, Section 5.7] which are here briefly reported.

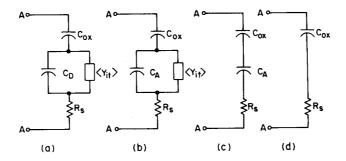

The series resistance can be measured considering the equivalent circuit of the MOS capacitor in depletion, as shown in figure 2.6a. At a given frequency, the greatest effect on the admittance is measured in strong accumulation. Figure 2.6b) shows the equivalent circuit of the MOS capacitor in strong accumulation, where the accumulation layer capacitance  $C_A$  is in parallel with  $\langle Y_{it} \rangle$ . The equivalent circuit can be simplified because  $C_A$  is large, shutting  $\langle Y_{it} \rangle$ , becoming that in figure 2.6c). Because  $C_A \gg C_{ox}$ , fig.2.6c) can be further simplified to figure 2.6d.

**Figure 2.6** (a) Equivalent circuit of the MOS capacitor in depletion including series resistance,  $R_S$ ; (b) Equivalent circuit of the MOS capacitor in strong accumulation; (c) simplified version of (b); (d) simplified version of (c) used in extracting values of  $C_{ox}$  and Rs from the admittance measured in strong accumulation [Nico82, figure 5.22].

To determine  $R_S$ , the MOS capacitor is biased into strong accumulation. The admittance  $Y_{ma}$  across the terminal A-A in figure 2.6d) in strong accumulation in terms of the capacitance  $C_{ma}$  and equivalent parallel conductance  $G_{ma}$  is:

$$Y_{ma} = G_{ma} + j\omega C_{ma} \tag{2.1}$$

Series resistance is the real part of the impedance  $Z_{ma}=1/Y_{ma}$  or:

$$R_{S} = \frac{G_{ma}}{G_{ma}^{2} + \omega^{2} C_{ma}^{2}}$$

(2.2)

Capacitance  $C_{ox}$  is obtained by substituting  $R_S$  from (2.2) into the relation  $C_{ma} = C_{ox}/(1 + \omega^2 R_S^2 C_{ox}^2)$  derived from the equivalent circuit in figure 2.6d) and solving for  $C_{ox}$ , which yields

$$C_{ox} = C_{\text{max}} \left[ 1 + \left( \frac{G_{ma}}{\omega C_{ma}} \right)^2 \right]$$

(2.3)

Corrected capacitance  $C_C$  and corrected equivalent parallel conductance  $G_C$  at the frequency of interest are:

$$C_{C} = \frac{\left(G_{m}^{2} + \omega^{2} C_{m}^{2}\right) C_{m}}{a^{2} + \omega^{2} C^{2}}$$

(2.4)

$$G_{c} = \frac{\left(G_{m}^{2} + \omega^{2} C_{m}^{2}\right) a}{a^{2} + \omega^{2} C_{m}^{2}}$$

(2.5)

where  $a = G_m - (G_m^2 + \omega^2 C_m^2) \cdot R_S$  and Cm and Gm are the capacitance and the equivalent parallel conductance measured across the terminal of the MOS capacitor.

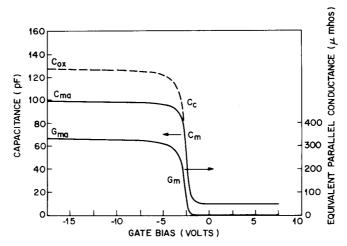

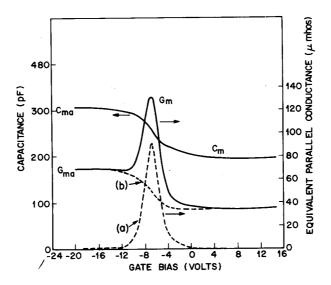

The effect of series resistance on capacitance and conductance is shown in figure 2.7 and 2.8, respectively. The absence of a peak in G(V) curve means that the device resistance produced the dominant loss, completely masking the interface trap loss.

The corrected capacitance,  $C_m$ , and the corrected conductance,  $G_m$ , obtained from (2.4) and (2.5) are show in figure 2.7 and 2.8, respectively (dotted line).

**Figure 2.7** Capacitance and equivalent conductance measured at 1MHz as a function of gate bias at a sweep rate of 10mV/sec. The capacitance corrected for series resistance is shown as the dashed curve [Nico82, figure 5.23].

**Figure 2.8** Capacitance and equivalent parallel conductance measured at 1MHz as a function of gate bias. The dashed conductance curve has been corrected for series resistance [Nico82, figure 5.24].

#### 2.2.2 Interface State Characterisation

The interface between silicon substrate and gate dielectric represents one of the crucial parameters that directly influence MOS devices performances. Standard silicon oxide gate dielectric thermally-grown from Si-substrate shows very low interface state density  $(D_{it})$ . Moving to high-k materials, the gate dielectric is grown by deposition on the Si-substrate.

Therefore a less perfect interface with silicon will be produced, leading to an increase of interface state density  $(D_{it})$ , which strongly affects the drive current of the device.

D<sub>it</sub> is one of the primary parameters used to characterise and monitor gate dielectric reliability and it also strongly correlates with the quality of the gate stack. A number of techniques have been developed for interface state measurements. In this research work, the conductance method first proposed by Nicollian and Goetzberger in 1967 and then developed by Brews [Brews83] has been used to characterise the interface properties of the MOS capacitors.

The Brew's method only need one curve  $(G_{it}/\omega\ vs.\ v_s)$  to extract the interface state density  $D_{it}$ , where  $G_{it}$  is the interface trap conductance,  $\omega$  the frequency in radians/sec and  $v_s$  the band bending. First of all, the capacitance and conductance measurements have to be corrected using the equation (2.4) and (2.5). After that, the interface trap conductance is calculated using the equation (2.6)

$$\frac{G_{it}}{\omega} = \frac{\omega C_{ox}^2 G_m}{G_m^2 + \omega^2 (C_{ox} - C_m)^2}$$

(2.6)

where  $C_m$  and  $G_m$  are the measured capacitance and conductance after correction. The interface state density is given by:

$$D_{it} = (G_{it} / \varpi)_p / (q^2 A f_D)$$

(2.7)

where  $(G_{it}/\varpi)_p$  is the maximum (peak) value of  $G_{it}/\omega$ , q is the elementary charge, A is the capacity area and  $f_D$  is a ratio that can be calculated as follow:

- starting from the graphic  $G_{it}/\omega$  vs.  $V_G$  and choosing the fraction of the width  $f_W$ , the  $V_G(+)$  and  $V_G(-)$  are extracted with respect to the  $(G_{it}/\varpi)_p$  peak position.

- $V_G(+)$ - $V_G(-)$  will be the entrance value in the band bending diagram ( $v_s$  vs.  $V_G$ ). In this way,  $v_s(+)$ - $v_s(-)$  can be read on the y-axe.

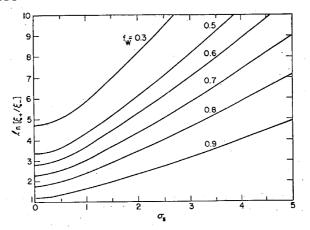

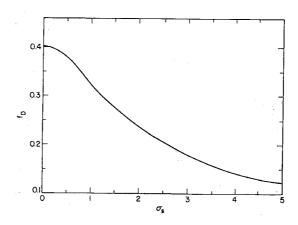

- $v_s(+)$ - $v_s(-)$  for the respective  $f_W$  allow the extraction of  $\sigma_s$  from figure 2.9 and  $f_D$  can be read from figure 2.10

**Figure 2.9** Experimental width parameter,  $\ln(\xi_+/\xi_-)$  vs. interfacial broadening parameter,  $\sigma_s$ , for various choices of the fractional value for the width,  $f_W$ . The width  $\ln(\xi_+/\xi_-)$  is  $v_s(+)-v_s(-)$ . [Brews83, figure 2].

**Figure 2.10** The ratio  $f_D$  vs.  $\sigma_s$ . [Brews83, figure 3].

#### 2.2.3 I(V) measurements

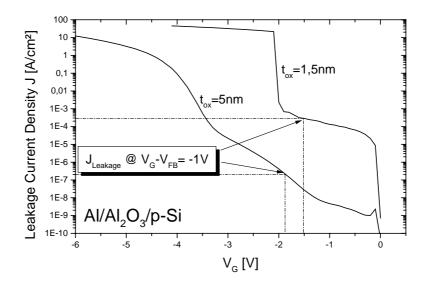

The measurement set-up used for I(V) measurement was a Keithley Picoammeter Type 487 in combination with a shielded 4-point-prober. The current resolution of this setup is about 1 nA/cm<sup>2</sup>. In order to filter leakage current from relaxation current the delay time between single measurement points is raised to 3-5 s for currents below 1 nA, while for currents above 1 nA the delay time is set to 250 ms.

Gate leakage current is normally used to characterise gate oxide and give important information about the conduction mechanism of the insulating layer. A list of the basic conduction processes is reported in table 2-2 ([Sze81], paragraph 7.3.4).

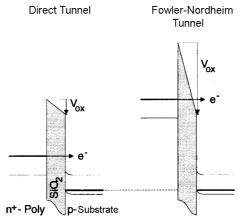

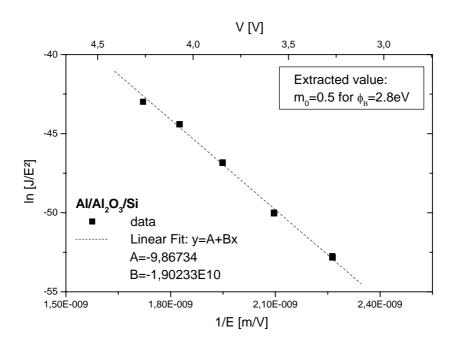

For an ultrathin insulator the dominating conduction mechanism is tunnelling through the gate dielectric. If the voltage applied on the gate electrode is lower than the metal barrier height, the electrons move from the metal Fermi level to the conduction band of the semiconductor through the total oxide thickness which is called Direct Tunneling. When the applied voltage  $(V_G)$  is higher than the barrier height of the metal gate, the electron will tunnel through a triangular barrier into the insulator conduction band. This conduction mechanism is called Fowler-Nordheim (FN) Tunneling. Direct tunnelling and FN tunnelling mechanism are illustrate inn fig. 2.11.

**Figure 2.11** Direct Tunnel and Fowler-Nordheim Tunnel for the electrons in a NMOS-structure having an n<sup>+</sup> doped polysilicon gate.

| Process                  | Expression                                                                                                        | Voltage and Temperature                    |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|                          |                                                                                                                   | Dependence                                 |

| Schottky emission        | $J = A \cdot T^{2} \exp \left[ \frac{-q \left( \phi_{B} - \sqrt{q\xi / 4\pi\varepsilon_{i}} \right)}{kT} \right]$ | $\sim T^2 \exp(+a\sqrt{V}/T - q\phi_B/kT)$ |

| Frenkel-Poole emission   | $J \sim \xi \exp \left[ \frac{-q \left( \phi_B - \sqrt{q  \xi  /  4 \pi \varepsilon_i}  \right)}{kT} \right]$     | $\sim V \exp(+2a\sqrt{V}/T - q\phi_B/kT)$  |

| Tunnel or field emission | $J \sim \xi^2 \exp \left[ -\frac{4\sqrt{2m^*}(q\phi_B)^{3/2}}{3q\hbar\xi} \right]$                                | $\sim V \exp(-b/V)$                        |

| Space-charge emission    | $J = \frac{8\varepsilon_i \pi V^2}{9d^3}$                                                                         | ~ V                                        |

| Ohmic                    | $J \sim \xi \exp(-\Delta E_{ae}/kT)$                                                                              | $\sim V \exp(-c/T)$                        |

| Ionic conduction         | $J \sim \frac{\xi}{T} \exp(-\Delta E_{ai} / kT)$                                                                  | $\sim \frac{V}{T} \exp(-d'/T)$             |

**Table 2-2** Conduction Mechanism in insulating films

$A^*=$ effettive Richarson constant,  $\phi_B=$ barrier height,  $\xi=$ electric field,  $\varepsilon_i=$ insulator permittivity,  $m^*=$ effective mass, d=insulator thickness,  $\Delta E_{ae}=$ activation energy of ions,  $a=\sqrt{q/(4\pi\varepsilon_i d)}$ , and  $V=\xi d$ . b, c and d' are positive constant independent of temperature (T) and voltage (V).

## 2.3. Physical and Chemical Characterisation Methods

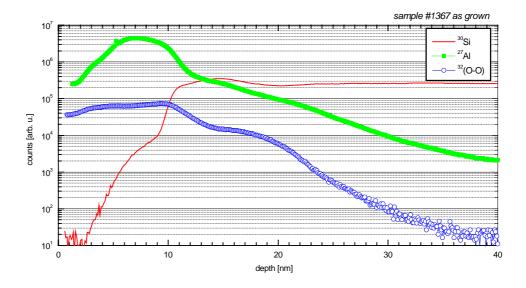

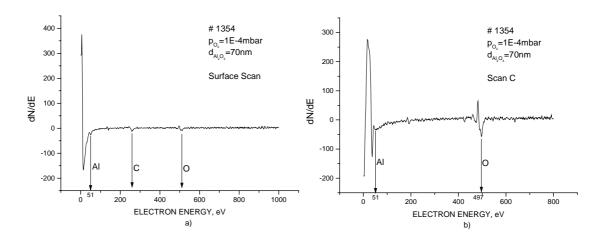

Chemical composition and physical structures of the gate stacks were studied by means of X-ray Photoelectron Spectrometry (XPS), Auger Electron Spectroscopy (AES), Rutherford Back Scattering Spectrometry (RBS) and high-resolution Transmission Electron Microscope (TEM).

### 2.3.1 X-ray Photoelectron Spectroscopy - XPS

X-ray photoelectron spectroscopy (XPS) is an analysis technique in surface and interface physics. It has its origins in the discovery of the photoelectric effect by Hertz [Dabr00], the energetic description given by Einstein and the publication of XP spectra for different metal by Robinson and Rawlinson. Starting from these study, Siegbahn et al. developed XPS in a sensitive, high resolution methods for the determination of the binding energy of the electrons. Today XPS is a standard technique capable to provide valuable information about the electronic structure in the film, also used to check the chemical composition and determine the stoichiometry of the sample.

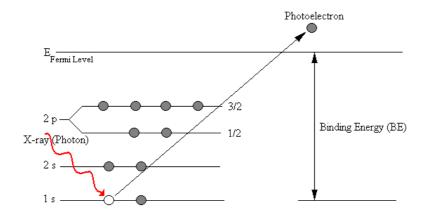

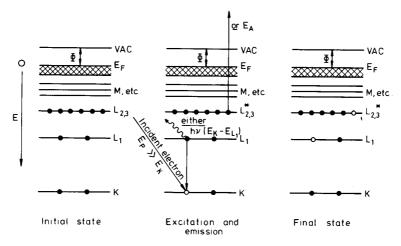

In XPS measurements, the radiation is usually obtained from x-ray tubes with Mg or Al anodes (Mg  $K\alpha$ -1253.6 eV, Al  $K\alpha$  –1486.6 eV). The XPS emission process is illustrated in figure 2.12. Photons interact with atoms in the surface region by photoelectric effect. A photoelectron ejected into the vacuum has an energy  $E_K$ =hv- $E_B$ - $\phi$ , where hv is the energy of the incoming photon,  $E_B$  is the atomic binding energy,  $\phi$  the work-function.

The measured photoelectron kinetic energy yields information about the binding energy of electrons and allows to identify different elements in the sample. Quantitative data can be obtained from peaks height or peaks areas, and identification of chemical state can be made

from the exact measurement of peak position. The mean free path of the escaping electron is usually in the range 5-20Å, which make XPS a surface sensitive technique.

In this thesis, the XPS analysis was performed in an ultrahigh vacuum Omicron XPS-system (base pressure  $5\cdot10^{10}$  mbar) equipped with an hemispherical electron energy analyser (EA 125) and a DAR 400 twin-anode X-ray source, where the X-ray source can be chosen between Al K $\alpha$  (energy 1486.6 eV) and Mg K $\alpha$  (energy 1253.6 eV). Since the Mg K $\alpha$  has a smaller full width at half maximum (FWHM) [OmiUG], i.e. a better analysis resolution, the Mg-anode was used for the reported measurements.

**Figure 2.12** XPS emission process: photons interact with atoms in the surface region by the photoelectric effect. A photoelectron ejected into the vacuum has an energy  $E_K=h\nu-E_B-\varphi$ , where  $h\nu$  is the energy of the incoming photon,  $E_B$  is the atomic binding energy,  $\varphi$  the work-function.

#### 2.3.2 Auger Electron Spectroscopy - AES

Auger Electron Spectroscopy (*Auger spectroscopy* or AES) is, like XPS, a surface sensitive technique that use emission of low energy electrons in the *Auger process* [Briggs, Lüth]. This technique was developed in the late 1960's and derives its name from the effect observed for the first time by Pierre Auger, French physicist, in the mid-1920's [Auge25]. AES is used to study the surface chemical composition (element analysis) as well as depth profiling of the concentration of chemical elements presents in the sample.

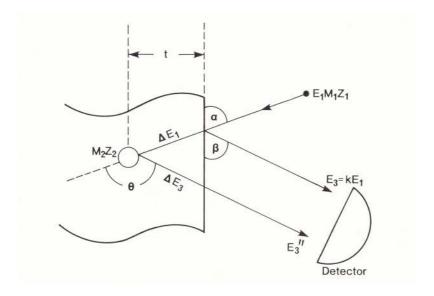

AES is a surface sensitive technique because of the limited escape depth of the electrons. Typical probing depth in AES are in the range 10-30 Å. The Auger process is explained in figure 2.13.

The basic Auger process starts with the removal of an inner shell atomic electron to form a vacancy. The excitation process is induced by exposing the sample to a beam of high energy electrons (typically having a primary energy in the range of 1 - 10 keV). Such electrons have sufficient energy to ionise all levels of the lighter elements and the core levels of the heavier elements. The inner shell vacancy is then filled by a second atomic electron from a higher shell. Since energy must be simultaneously released, a third electron, the Auger electron, escape carrying the excess energy in a radiation-less process. The process of an excited ion decaying into a doubly charged ion by ejection of an electron is called Auger process. Alternatively, the energy can be removed by an X-ray photon. For low atomic number elements the most probable transitions occur when a K-level electron is ejected by the primary beam, an L-level drops into the vacancy and another L-level

electron is ejected. For elements having higher atomic number LMM and MNN transition are more probable than KLL. As consequence, secondary electrons having sharply-defined energy are emitted. These can be than detected and analysed by electron analyser like for example Cylindrical Mirror Analyser (CMA).

In general the initial ionisation is a non-selective process and there will be many possible Auger transitions for a given element. Auger Spectroscopy is based upon the measurement of the kinetic energies of the emitted electrons. Each element of the analysed sample will give rise to a characteristic spectrum of peaks at various kinetic energy directly related to the differences in core-level energies: measuring these kinetic energies allows to identify the particular elements present in the sample, making exception of hydrogen and helium which have only one shell.

Figure 2.13 A schematic example of an Auger emission process. The system in its the ground state is reported on the left. In the centre an incident electron has created a hole in the core level K by ionisation. The hole of the K shell is filled by an electron from  $L_1$ , releasing an amount of energy which can appear as a photon or can be given up to another electron as in this case. The doubly ionised final state is shown on the right. After [Brig85]

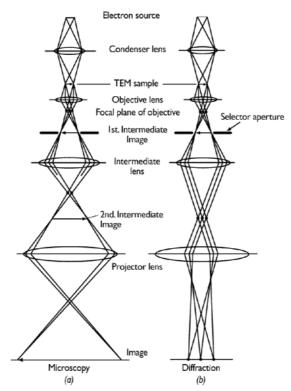

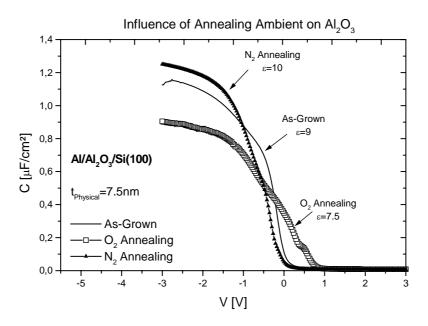

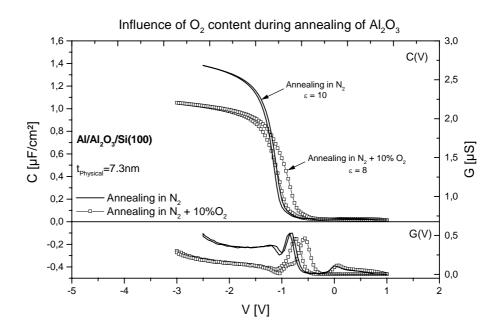

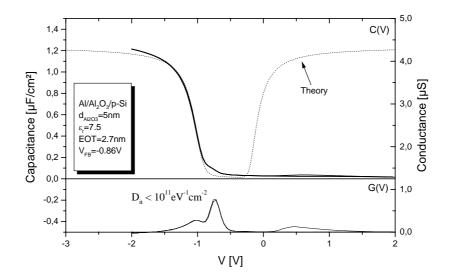

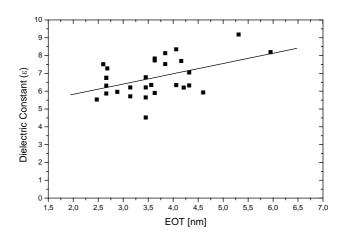

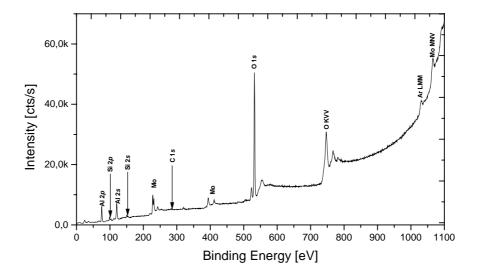

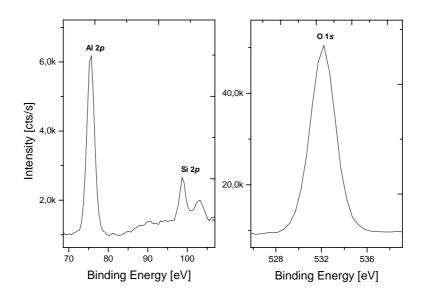

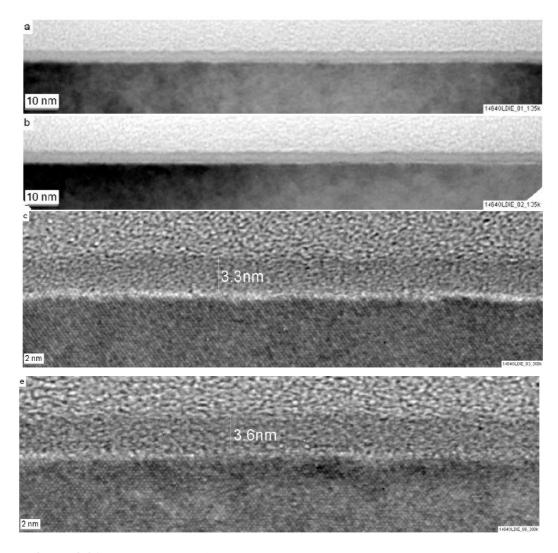

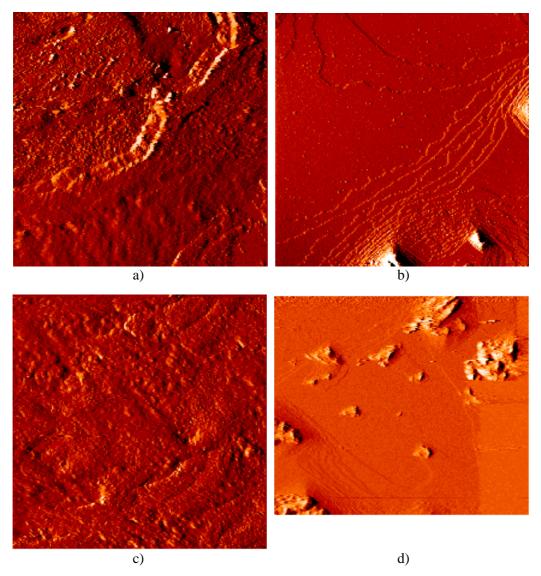

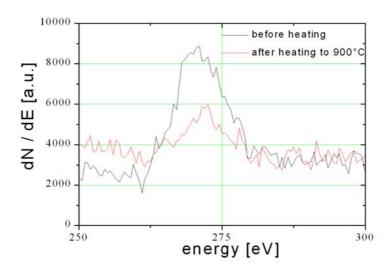

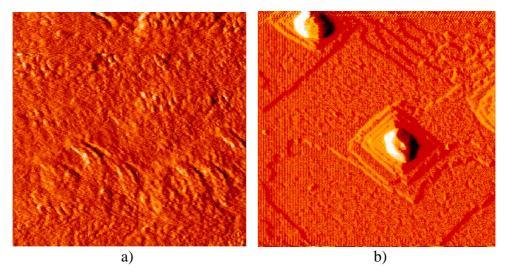

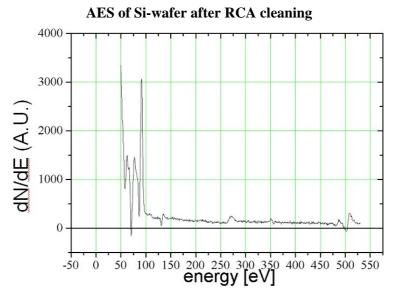

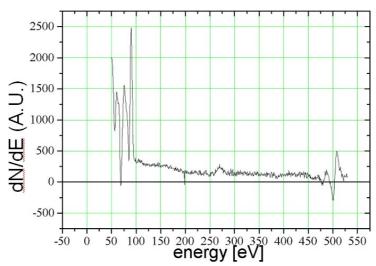

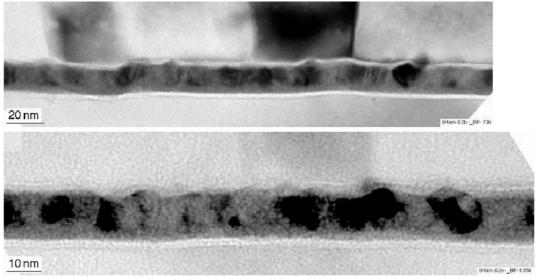

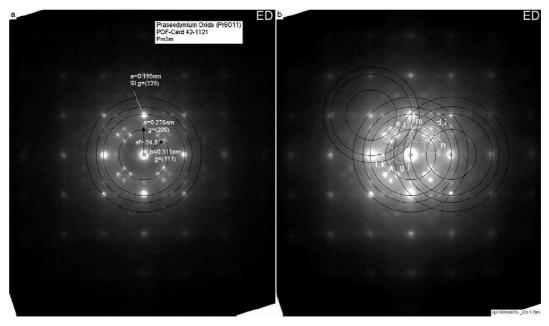

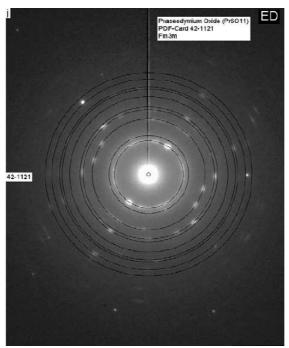

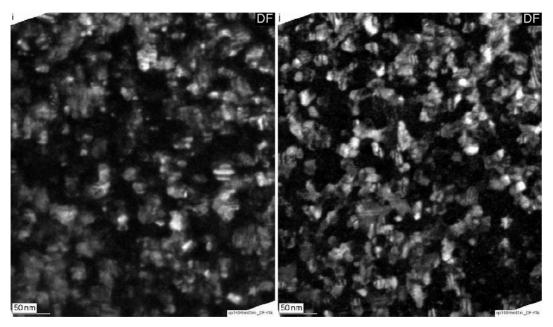

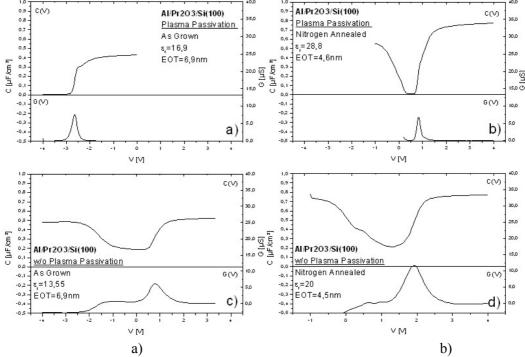

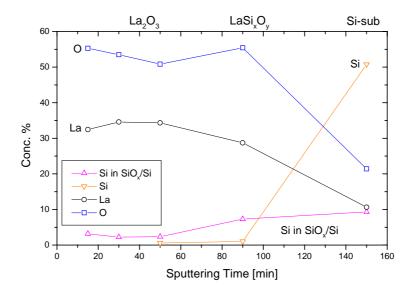

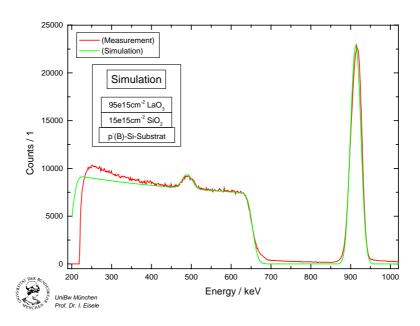

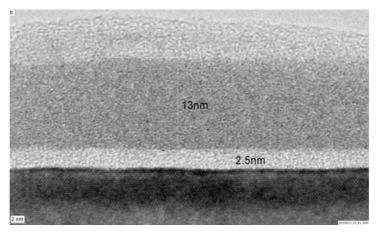

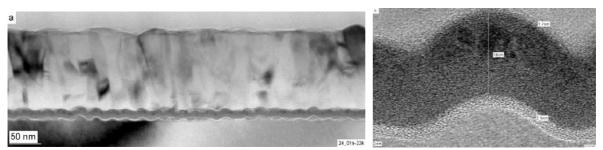

#### 2.3.3 Rutherford BackScattering Spectroscopy - RBS